# SRAM DATA BOOK

# SRAM DATA BOOK

2805 East Columbia Road Boise, Idaho 83706 Telephone: (208) 368-3900 FAX: (208) 368-4431 Customer Comment Line: (800) 932-4992

©1991, Micron Technology, Inc. Printed in the U.S.A.

Micron Technology, Inc., reserves the right to change products or specifications without notice.

### **ABOUT THE COVER:**

Front—Clockwise from left, 1) Micron's Cache Data SRAM wafer; 2) Micron team members build quality into every Micron wafer at our Boise, Idaho, facilities; 3) a SEM photograph of the SRAM lithography process; and 4) Micron's packaged SRAMs in SOJ, PQFP and SOIC packages.

Back — Micron's Boise, Idaho, headquarters.

### **IMPORTANT NOTICE**

Micron Technology, Inc., reserves the right to change products or specifications without notice. Customers are advised to obtain the latest versions of product specifications, which should be considered in evaluating a product's appropriateness for a particular use. There is no assurance that Micron's semiconductors are appropriate for any application by a customer.

MICRON TECHNOLOGY, INC., MAKES NO WARRANTIES EX-**PRESSEDOR IMPLIED OTHER THAN** COMPLIANCE WITH MICRON'S SPECIFICATION SHEET FOR THE COMPONENT AT THE TIME OF DELIVERY. ANY CLAIM AGAINST MICRON MUST BE MADE WITHIN NINETY (90) DAYS FROM THE DATE OF SHIPMENT FROM MICRON, AND MICRON HAS NO LIABILITY THEREAFTER. ANY MICRON LIA-BILITY IS LIMITED TO REPLACE-MENT OF DEFECTIVE ITEMS OR **RETURN OF AMOUNTS PAID FOR** DEFECTIVE ITEMS (AT THE BUYER'S ELECTION).

MICRON'S PRODUCTS ARE NOT AUTHORIZEDFORUSEASCRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF MICRON TECHNOLOGY, INC. AS USED HEREIN:

A. LIFE SUPPORT DEVICES OR SYSTEMS ARE DEVICES OR SYS-TEMS WHICH (1) ARE INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR (2) SUPPORT OR SUSTAIN LIFE AND WHOSE FAILURE TO PERFORM WHEN PROPERLY USED IN ACCORDANCE WITH INSTRUC-TIONS FOR USE PROVIDED IN THE LABELING CAN BE REASONABLY EXPECTED TO RESULT IN A SIGNIFICANT INJURY TO THE USER.

B. CRITICAL COMPONENT IS ANY COMPONENT OF A LIFE SUPPORT DEVICE OR SYSTEM WHOSE FAILURE TO PERFORM CAN BE REASONABLY EXPECTED TO CAUSE THE FAILURE OF THE LIFE SUPPORT DEVICE OR SYSTEM OR TO AFFECT ITS SAFETY OR EFFECTIVENESS.

i

# MICRON

### ADVANTAGES

Quality, productivity and innovation unite at Micron. Because of our emphasis on quality, we have created hundreds of reliable, high-performance memory products. Our products feature some of the industry's fastest speeds and smallest die sizes, delivered when you need them, and reliable beyond your expectations. And, because we produce our products in a centralized location, we can offer unparalleled flexibility and project control.

### COMPONENT INTEGRATED CIRCUITS

Micron Technology entered the memory market 14 years ago to manufacture dynamic random access memory (DRAM). From there, we developed high-performance fast static RAM (SRAM), multiport DRAM (VRAM and Triple Port DRAM), and a variety other memory products.

As we bring progressive memory solutions to our customers, we enjoy recognition for our achievements. Micron's Triple Port DRAM was the first IC ever to incorporate a second, independent serial access port, allowing unparalleled flexibility in data manipulation. In 1990, Micron's Triple Port received the 1990 "Product of the Year" award from *Electronic Products* magazine.

### SPECIALTY MEMORY PRODUCTS

Beyond our standard component memory, Micron is introducing many revolutionary products that we expect will follow the Triple Port's tradition. From FIFOs to processors, Micron continues to forge ahead into new and exciting frontiers.

We are pleased to be first to market with our compact, easy-to-install IC DRAM Card. Ideal for laptop, notebook and other portable systems, Micron's IC DRAM Card offers both high density and low power within JEDEC and JEIDA specifications.

### MILITARY CERTIFIED PRODUCTS

As one of the few manufacturers of military-grade memory in North America, Micron is proud to provide a documented source inspection from wafer start to finished product. We've earned recognition from U.S. and European space agencies as well as Joint Army/Navy certification for both our NMOS and CMOS process technologies.

### **DIE SALES**

In addition to our durable ceramic packaging, Micron also provides memory devices in bare die form. These are increasingly in demand for commercial and military use in highly specialized applications. Micron's bare dice are available in 6" wafers and wafflepacks.

#### **OEM SYSTEM-LEVEL PRODUCTS**

For total project management, Micron offers added value services. These include both standard contract manufacturing of system-level products from any single phase — design, assembly, customer kitted assembly, comprehensive quality testing or shipping — and complete turnkey services covering all phases of production. Our component and system-level manufacturing facilities are centrally located in Boise, Idaho, so any reliable component products you may need for your board are readily available.

### QUALITY

Without a doubt, the most important thing we provide goes out to every Micron customer with every Micron product — quality. That's because we believe that quality must be internalized at every level of our company. We're committed to our employees as well as our customers. We provide every Micron team member with the tools, confidence and motivation they need to make Micron's quality philosophy a reality.

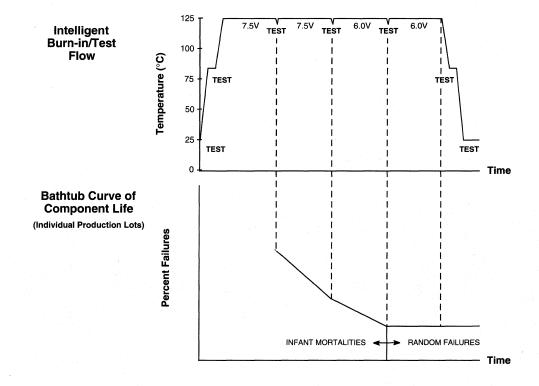

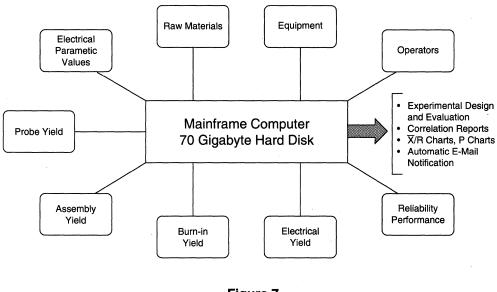

One way we have measurably improved both productivity and product quality is through our quality improvement teams. These groups of Micron team members get together to address a wide range of issues within their areas. We've also implemented statistical process controls to evaluate every facet of the memory design, fabrication, assembly and shipping process. And our AMBYX<sup>™</sup> intelligent burn-in and test system<sup>\*</sup> gives Micron the ultimate edge in product reliability. \*For more information on Micron's AMBYX<sup>™</sup>, see Section 7.

### **GENERAL INFORMATION**

Micron Technology, Inc., is dedicated to the design, manufacture and marketing of high quality, highly reliable memory integrated circuits. Our corporate mission is:

# "To be a world class team developing advantages for our customers"

At Micron, we are investing time, talent and resources to bring you the finest DRAMs, SRAMs, VRAMs and other specialty memory products. We have developed a unique intelligent burn-in system, the AMBYX<sup>™</sup>, that evaluates and reports the quality level of each and every component we produce.

We are dedicated to continuous improvement of all our products and services. This means continual reduction of electrical and mechanical defect levels. It also means the addition of new services such as "just-in-time" delivery and electronic data interchange programs. And, when you have a design or application question, you can get the answers you need from the source — one of Micron's applications engineers.

We're proud of our products, our progress and our performance. And we're pleased that you're choosing Micron as your memory supplier.

The Micron Team

### **GENERAL INFORMATION**

### **ABOUT THIS BOOK**

#### CONTENT

The 1992 *SRAM Data Book* from Micron Technology provides complete specifications on all standard SRAMs and SRAM modules as well as specialty and derivative products based on our SRAM production process.

The SRAM Data Book is one of three product data books Micron publishes. Its two companion volumes include our DRAM Data Book (to be released in February/March 1992) and Military Data Book (currently available).\*

#### SECTION ORGANIZATION

Micron's 1992 *SRAM Data Book* contains a detailed Table of Contents with sequential and numerical indexes of products as well as a complete product selection guide. The Data Book is organized into nine sections:

- Sections 1–5: Individual product families. Contains a product selection guide followed by data sheets.

- Section 6: Application information.

- Section 7: Summary of Micron's unique quality and reliability programs and testing operation, including our AMBYX<sup>™</sup> intelligent burn-in and test system.\*\*

- Section 8: Packaging information.

- Section 9: Product ordering information, including a list of sales representatives and distributors worldwide.

#### DATA SHEET SEQUENCE

Data sheets in this book are ordered by width first and depth second. For example, the SRAM section begins with the 16K x 1 SRAM followed by 64K x 1 and all other x1 configurations in order of ascending depth. Next come the x4 products, followed by x8, etc., as applicable to the specific product family.

#### DATA SHEET DESIGNATIONS

As detailed below, each Micron product data sheet is classified as either **Advance**, **Preliminary** or **Final**. In addition, new product data sheets that are new additions to this data book are designated with a "New" in the tab area of the front page.

#### SURVEY

We have included a removable, postage-paid survey form in the front of this book. Your time in completing and returning this survey will enhance our efforts to continually improve our product literature.

For more information on Micron product literature, or to order additional copies of this publication, contact:

Micron Technology, Inc. 2805 East Columbia Road Boise, ID 83706 Phone: (208) 368-3900 FAX: (208) 368-4431 Customer Comment Line: (800) 932-4992

| DATA SHEET MARKING | DEFINITION                                                                                                                                                                                                                                                                                   |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Advance"          | This data sheet contains initial descriptions of products still under development.                                                                                                                                                                                                           |

| "Preliminary"      | This data sheet contains initial characterization limits that are subject to change upon full characterization of production devices.                                                                                                                                                        |

| No Marking (Final) | This data sheet contains minimum and maximum limits specified over the complete power supply and temperature range for production devices. Although considered final, these specifications are subject to change, as further product development and data character-ization sometimes occur. |

| "New"              | This data sheet (which may be either Advance, Preliminary or Final) is a new addition to the Data Book.                                                                                                                                                                                      |

### DATA SHEET DESIGNATORS

\* For complete information on Micron's Military Products, send for our *Military Data Book* by calling Micron Technology, Inc. \*\* Micron's *Quality/Reliability Handbook* is available by calling the number listed above.

### **GENERAL INFORMATION**

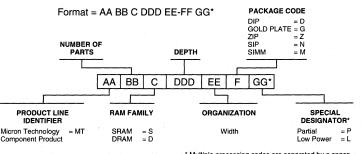

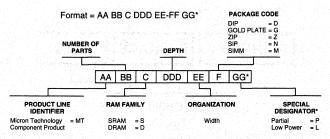

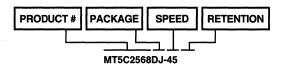

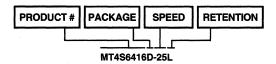

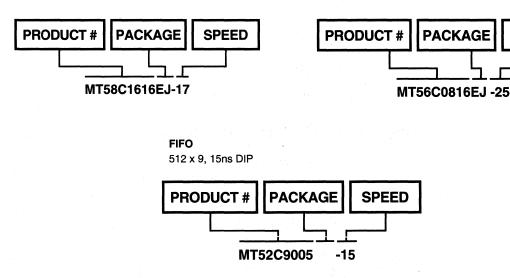

### COMPONENT PRODUCT NUMBERING SYSTEM

### MODULE PRODUCT NUMBERING SYSTEM

\* Multiple processing codes are separated by a space. Listed in hierarchy in case of multiple options.

### STATIC RAMS

MICRON

### PAGE

| MT5C160116K x 1                                                         | CE only                                                                                                        | 1-1       |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|

| MT5C640164K x 1                                                         | CE only                                                                                                        |           |

| MT5C2561256K x 1                                                        | $\overline{\text{CE}}$ only                                                                                    |           |

| MT5C10011 Meg x 1                                                       | CE only                                                                                                        |           |

| MT5C16044K x 4                                                          |                                                                                                                |           |

| MT5C16054K x 4                                                          |                                                                                                                | 1-41      |

| MT5C16064K x 4                                                          | SI/O, OT                                                                                                       | 1-49      |

| MT5C16074K x 4                                                          | SI/O, HZ                                                                                                       | 1-49      |

| MT5C640416K x 4                                                         | CE only                                                                                                        | 1-57      |

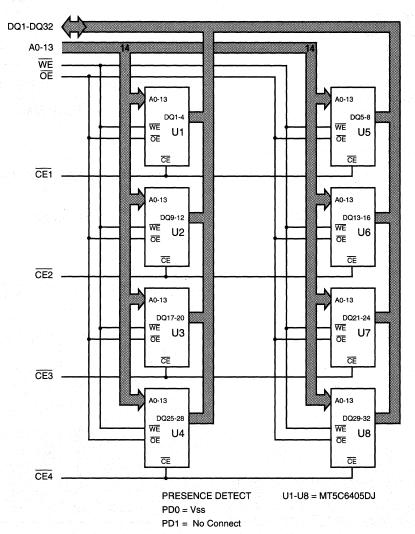

| MT5C6405                                                                | CE & ÓE                                                                                                        | 1-65      |

| MT5C6406                                                                | $SI/O, \overline{CE1}, \overline{CE2}, \overline{OE} \& OT$                                                    |           |

| MT5C640716K x 4                                                         | SI/O, HZ                                                                                                       |           |

| MT5C256464K x 4                                                         |                                                                                                                |           |

| MT5C256564K x 4                                                         | $\overline{CE} \& \overline{OE}$                                                                               | 1-89      |

| MT5C1005256K x 4                                                        | $\overline{CE} \& \overline{OE}$                                                                               | 1-97      |

| MT5C40051 Meg x 4                                                       |                                                                                                                | 1-105     |

| MT5C41051 Meg x 4                                                       | $\overline{CE} \& \overline{OE}$                                                                               | 1-107     |

| MT5C16082K x 8                                                          | $\overline{CE} \& \overline{OE}$                                                                               | 1-109     |

| MT5C64088K x 8                                                          | $\overline{\text{CE1}}$ , CE2 & $\overline{\text{OE}}$                                                         | 1-117     |

| MT5C2568                                                                | $\overline{CE} \& \overline{OE}$                                                                               | 1-125     |

| MT5C1008128K x 8                                                        | $\overline{\text{CE1}}$ , CE2 & $\overline{\text{OE}}$                                                         | 1-133     |

| MT5C1009128K x 8                                                        | $\overline{CE} \& \overline{OE}$                                                                               | 1-141     |

| MT5C4008512K x 8                                                        | $\overline{CE} \& \overline{OE}$                                                                               | 1-149     |

| MT5C4108512K x 8                                                        | $\overline{CE} \& \overline{OE}$                                                                               |           |

| MT5C2889                                                                | $\overline{\text{CE1}}$ , CE2 & $\overline{\text{OE}}$                                                         | 1-153     |

| MT5C1189128K x 9                                                        | $\overline{CE} \& \overline{OE}$                                                                               | 1-161     |

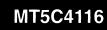

| MT5C4116                                                                | $\overline{CE} \& \overline{OE}$                                                                               | 1-169     |

| IT/AT/XT SPECIFICATIONS                                                 |                                                                                                                | 1-171     |

|                                                                         |                                                                                                                |           |

| 그는 것 같은 것 같은 것 같은 것 같은 것 같은 것 않는 것 같은 것 같 | land fan de geleger fan de fan fan de fan ferste fan de fan d | 1. Sec. 1 |

| CE |                                   |

|----|-----------------------------------|

| OE | OUTPUT ENABLE                     |

| ОТ | OUTPUTS TRACK INPUTS DURING WRITE |

SI/O ......SEPARATE DATA INPUTS AND OUTPUTS HZ ......HIGH IMPEDANCE OUTPUTS DURING WRITE

### SYNCHRONOUS SRAMS

| MT58C1289 | 128K x 9 |

|-----------|----------|

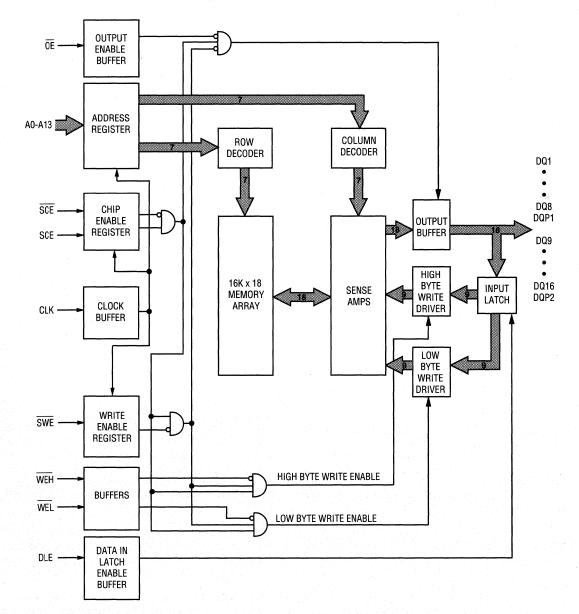

| MT58C1616 | 16K x 16 |

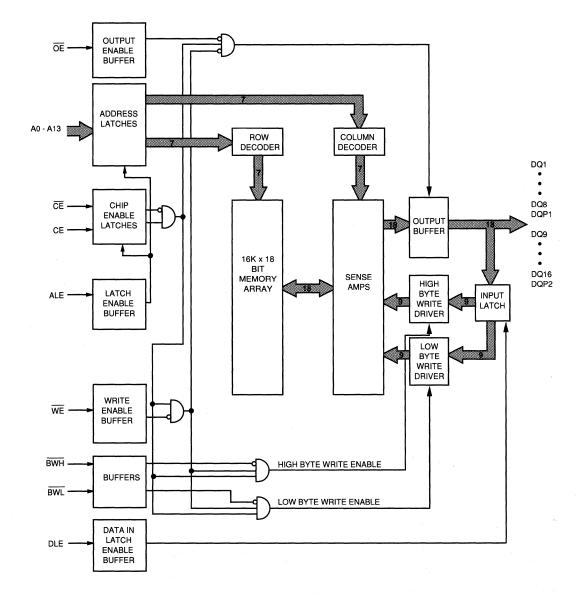

| MT58C1618 | 16K x 18 |

| SR   | SYNCHRONOUS READS            |

|------|------------------------------|

| DSCE | DUAL SYNCHRONOUS CHIP ENABLE |

| BW   | BYTE WRITE                   |

| SR, STW, DSCE, SWE, OE | 2-1  |  |

|------------------------|------|--|

| SR, STW, DSCE, OE, BW  | 2-11 |  |

| SR, STW, DSCE, OE, BW  | 2-21 |  |

|                        |      |  |

OTHE DOOD OWN OF

| STW | SELF-TIMED WRITES |

|-----|-------------------|

|     |                   |

|     |                   |

$\begin{array}{c} \overline{CE} \& \overline{OE} & & 3-1 \\ \overline{CE} \& \overline{OE} & & 3-9 \\ \overline{CE} \& \overline{OE} & & 3-17 \\ \overline{CE} \& \overline{OE} & & 3-25 \\ \overline{CE} \& \overline{OE} & & 3-25 \\ \overline{CE} \& \overline{OE} & & 3-33 \\ \overline{CE} \& \overline{OE} & & 3-41 \\ \overline{CE} \& \overline{OE} & & 3-49 \\ \end{array}$

### **SRAM MODULES**

| MT4S1288  | 128K x 8    |

|-----------|-------------|

| MT2S3216  |             |

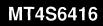

| MT4S6416  | 64K x 16    |

| MT8S1632  | 16K x 32    |

| MT8S6432  | 64K x 32    |

| MT4S12832 |             |

| MT8S25632 | 256K x 32   |

| СЕ        | CHIP ENABLE |

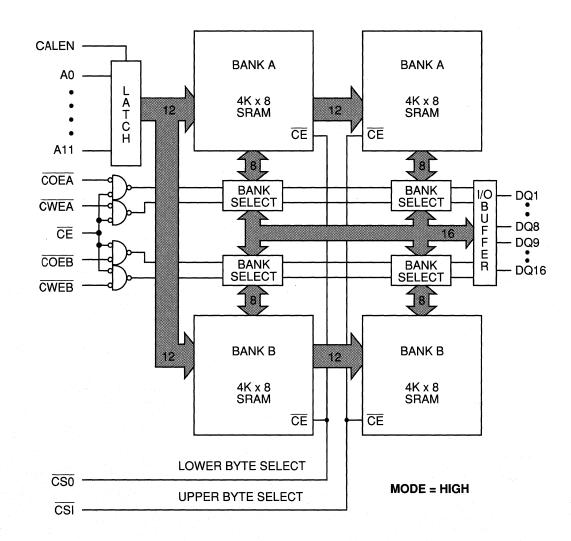

### CACHE DATA/LATCHED SRAMS

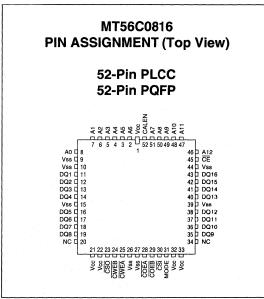

| MT56C0816 Dual 4K x 1 | 6 or Single 8K x 16 |

|-----------------------|---------------------|

| MT56C3816 Dual 4K x 1 | 6 or Single 8K x 16 |

| MT5C2516              | 16K x 16            |

| MT56C0818 Dual 4K x 1 | 8 or Single 8K x 18 |

| MT56C2818 Dual 4K x 1 | 8 or Single 8K x 18 |

| MT56C3818 Dual 4K x 1 | 8 or Single 8K x 18 |

| MT5C2818              |                     |

|                       |                     |

| A0-A11 Latch, BS, CE & OE                                          | 4-1  |

|--------------------------------------------------------------------|------|

| A0-A12 Latch, BS, $\overline{CE} \& \overline{OE}$                 | 4-13 |

| $LA/Data, BW, DCE, \overline{CE} \& \overline{OE}$                 | 4-25 |

| A0-A11 Latch, BS, $\overline{CE} \& \overline{OE}$                 |      |

| $80486/80485$ Specific, BS, SWE, $\overline{CE}$ , $\overline{OE}$ | 4-51 |

| A0-A12 Latch, BS, $\overline{CE} \& \overline{OE}$                 |      |

| $LA/Data, BW, DCE, \overline{CE} \& \overline{OE}$                 | 4-73 |

|                                                                    |      |

| CE      | CHIP ENABLE              |

|---------|--------------------------|

| OE      | OUTPUT ENABLE            |

| BW      | BYTE WRITE               |

| LA/Data | LATCHED ADDRESS AND DATA |

| DCE | DUAL CHIP ENABLE         |

|-----|--------------------------|

| SWE | SYNCHRONOUS WRITE ENABLE |

| BS  | BYTE SELECT              |

# PAGE

PAGE

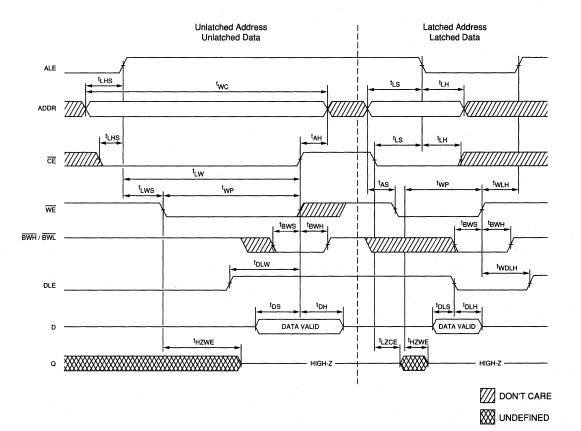

### FIFO (FIRST-IN FIRST-OUT) MEMORIES

MICRON

| MT52C9005 |                            | Е     |                 | 5-1  |

|-----------|----------------------------|-------|-----------------|------|

|           |                            |       |                 |      |

| MT52C9010 | 1K x 9                     | Е     |                 | 5-29 |

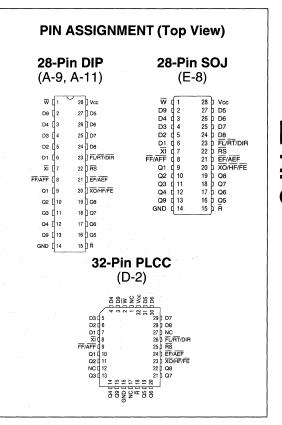

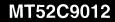

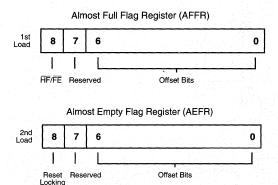

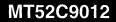

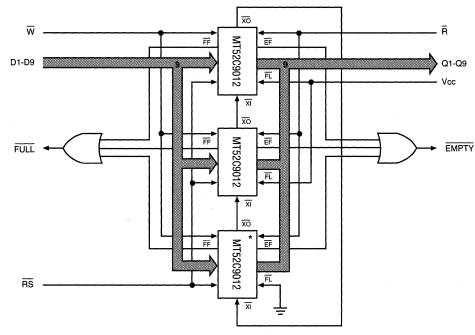

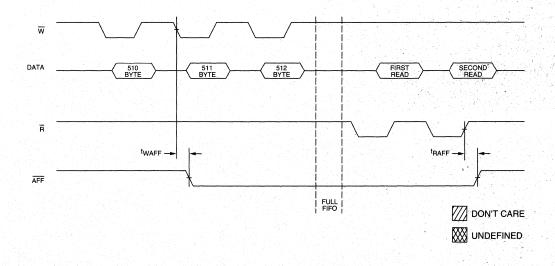

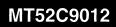

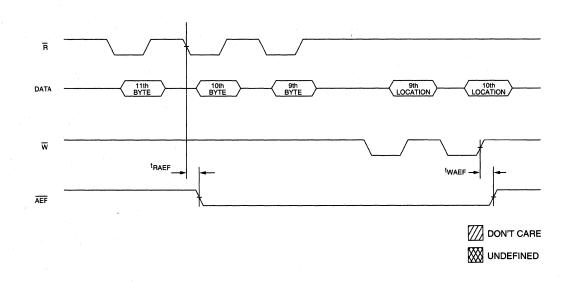

| MT52C9012 | 1K x 9                     | PF, E | 5               | 5-41 |

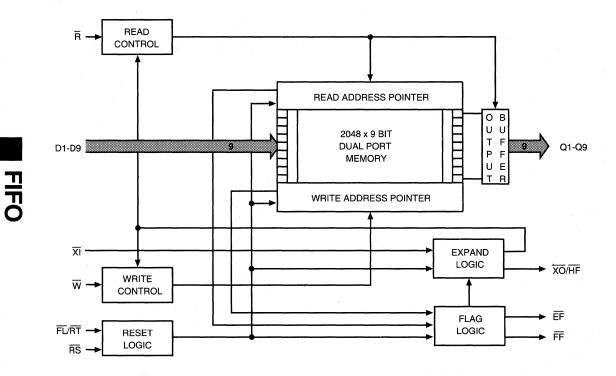

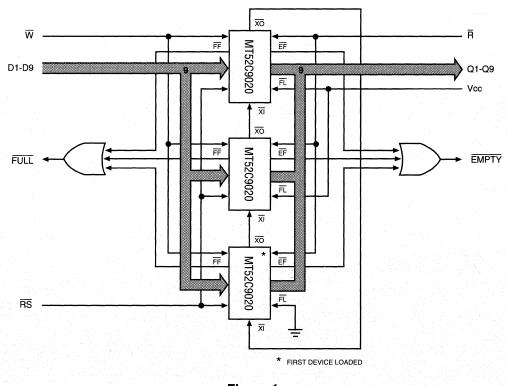

| MT52C9020 | 2K x 9                     | Е     | ΕΕ              | 5-57 |

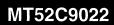

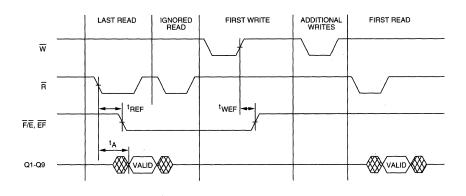

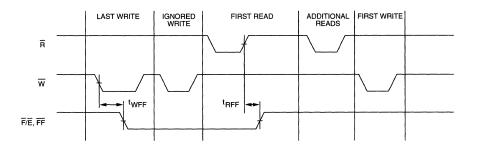

| MT52C9022 | 2K x 9                     | PF, E |                 | 5-69 |

|           | EXPANDABLE DEPTH AND WIDTH |       |                 |      |

| Е         | EXPANDABLE DEPTH AND WIDTH | PF    | PROGRAMMABLE FL | AG   |

### APPLICATION/TECHNICAL INFORMATION

| TN-00-01 | Moisture Absorption in Plastic Packages   | 6-1  |

|----------|-------------------------------------------|------|

|          | Micron Tape and Reel Procedures           |      |

|          | SRAM Bus Contention Design Considerations |      |

|          | SRAM Capacitive Loading                   |      |

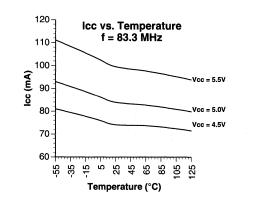

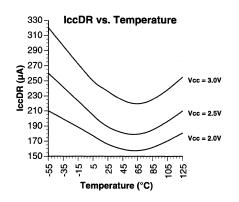

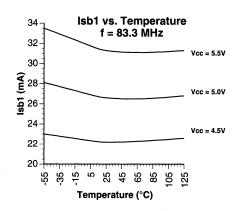

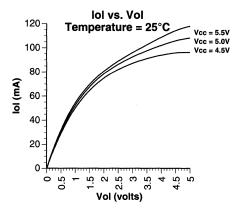

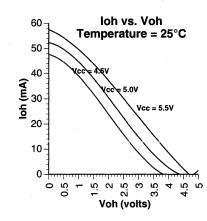

|          | 1 Meg Fast SRAM Typical Operating Curves  |      |

|          | 256K Fast SRAM Typical Operating Curves   |      |

|          |                                           |      |

|          | 128K x 8 SRAM Chip Enable Options         |      |

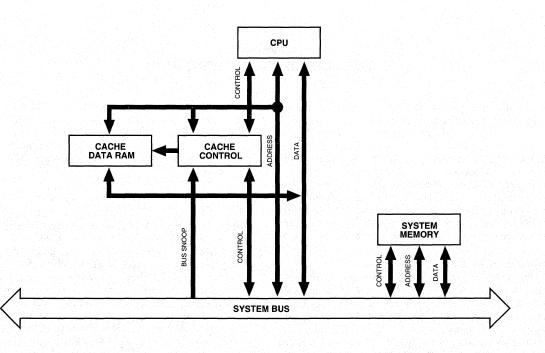

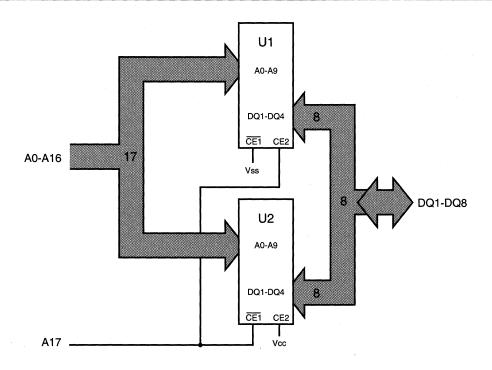

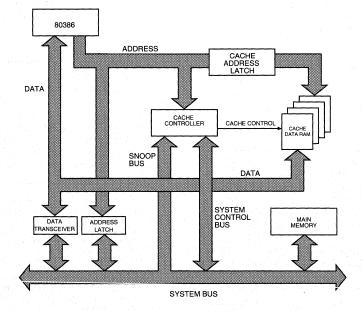

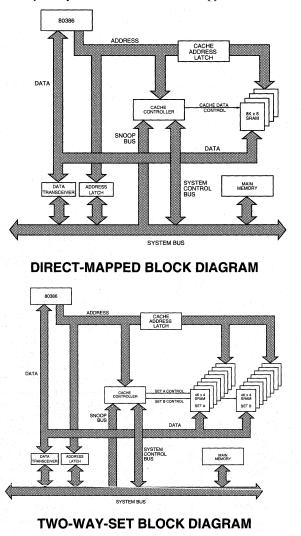

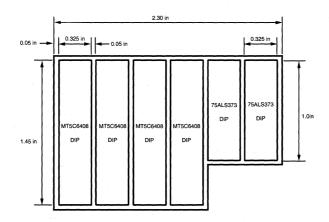

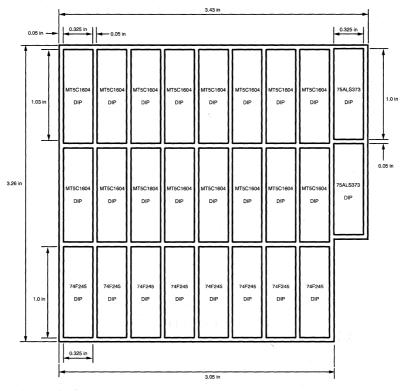

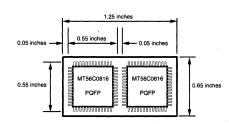

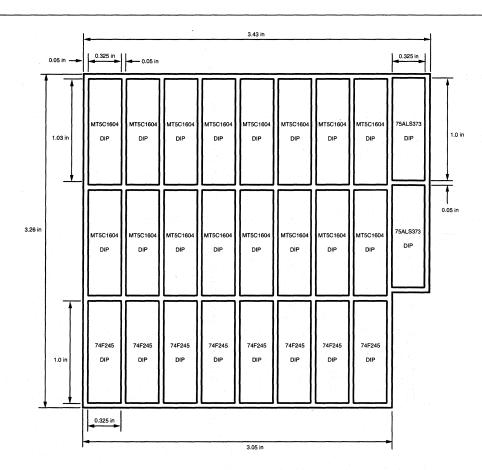

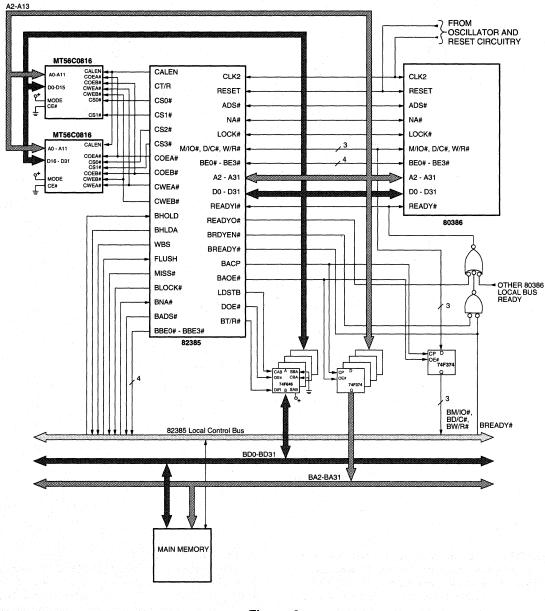

| AN-56-01 | MT56C0816 Cache Data SRAM Family          | 6-23 |

|          |                                           |      |

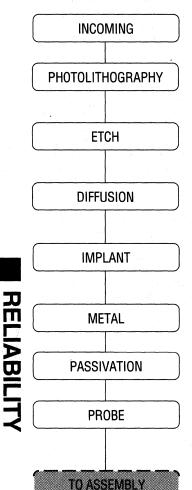

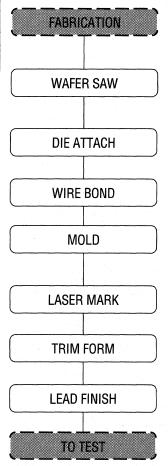

### **PRODUCT RELIABILITY**

| Product Reliability | <br> |

|---------------------|------|

| Process Flow Chart  | <br> |

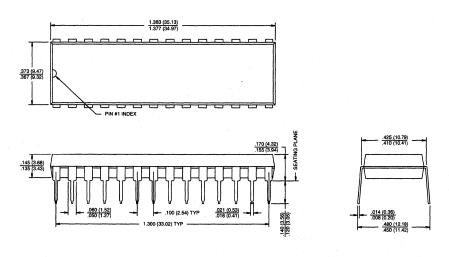

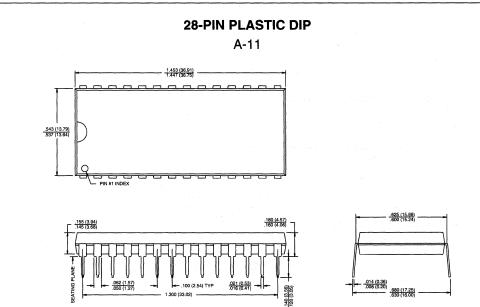

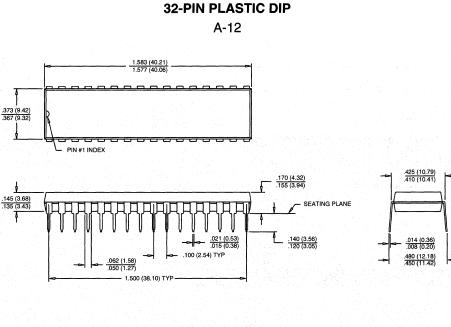

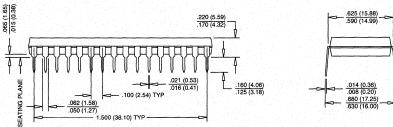

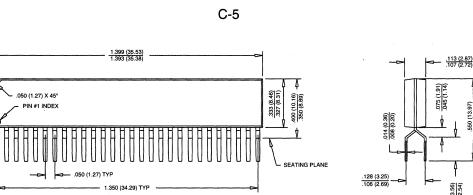

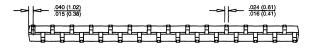

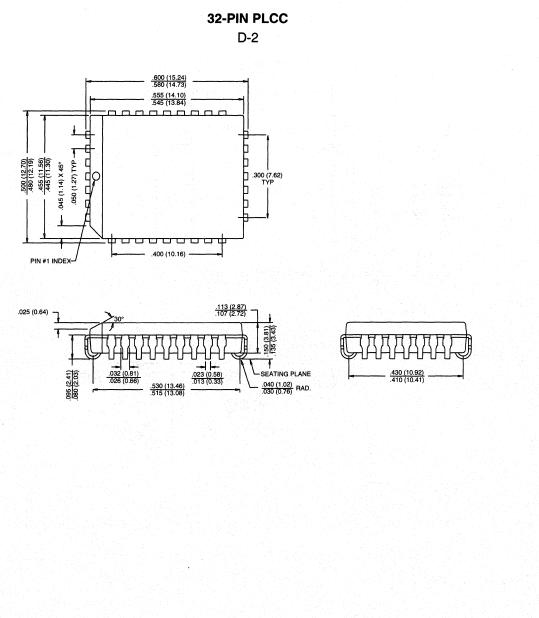

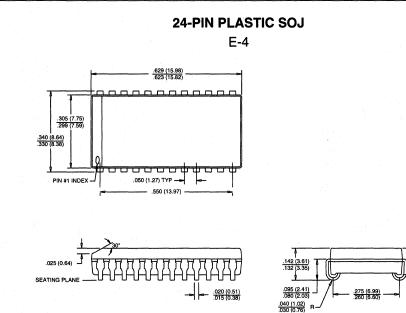

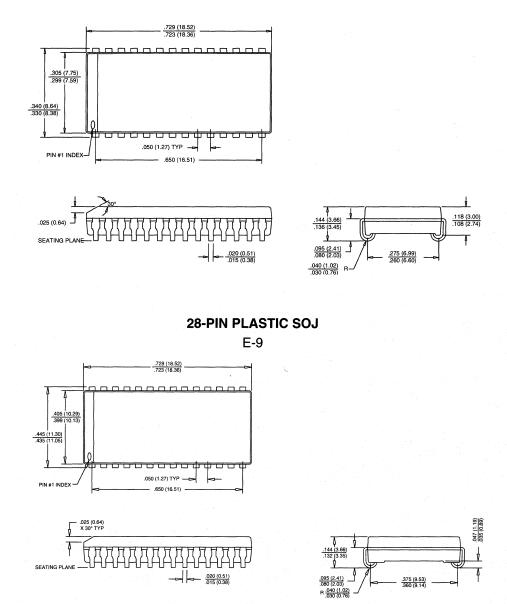

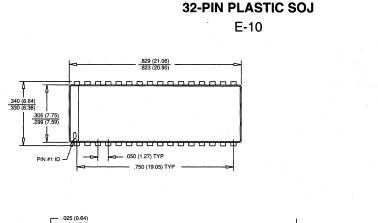

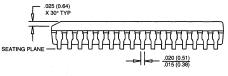

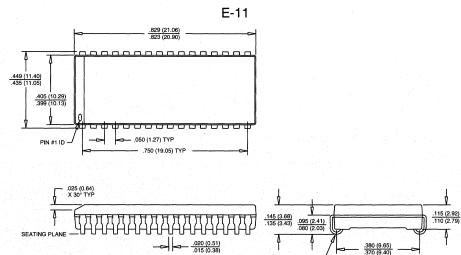

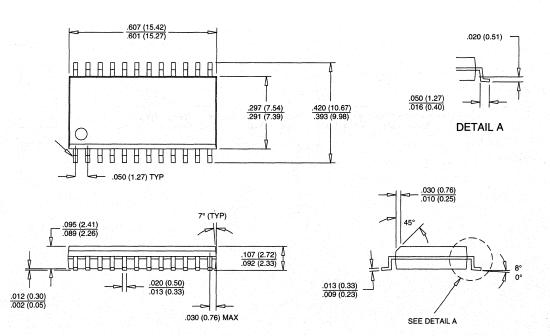

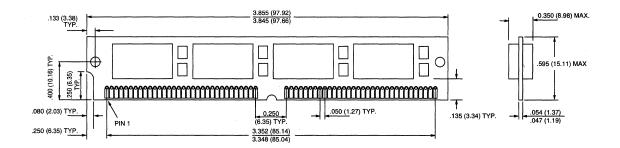

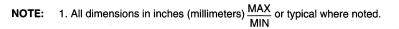

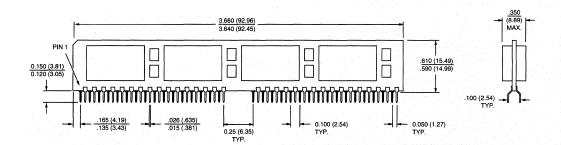

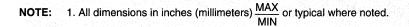

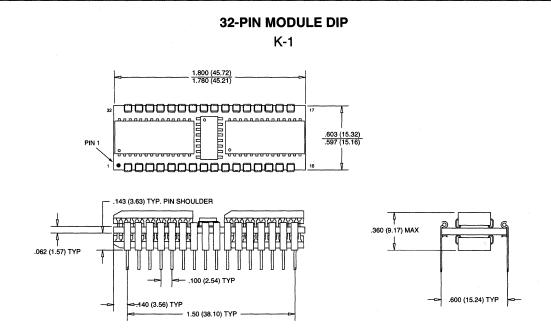

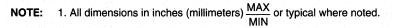

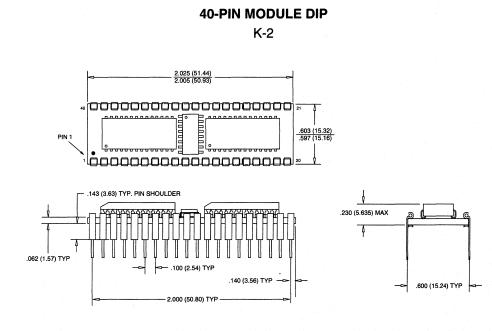

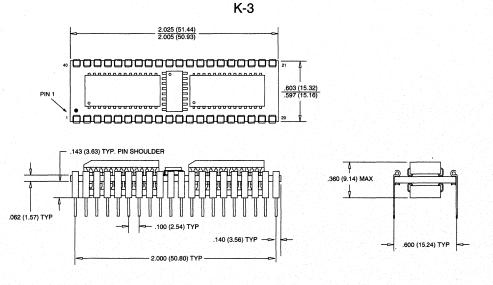

### **PACKAGE INFORMATION**

| Index            |        |       |

|------------------|--------|-------|

| Package Drawings | •••••• | <br>; |

### SALES INFORMATION

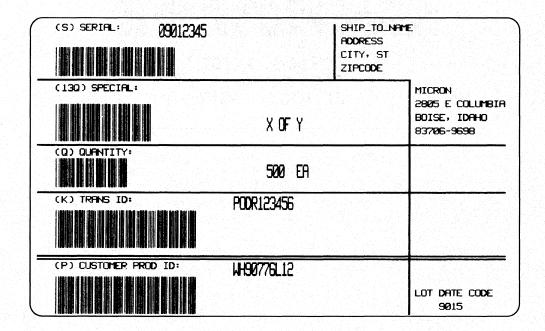

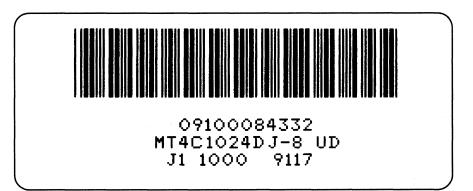

| Customer Service Notes                                |       | 9-1  |

|-------------------------------------------------------|-------|------|

| Product Numbering System                              |       | 9-3  |

| Ordering Information and Examples                     |       | 9-4  |

| North American Sales Representatives and Distributors | ••••• | 9-5  |

| International Sales Representatives and Distributors  | ••••• | 9-18 |

# NUMERICAL INDEX

### PAGE

| Part #  |                                                                                                                 |      |

|---------|-----------------------------------------------------------------------------------------------------------------|------|

| 2S3216  | SRAM MODULE .                                                                                                   |      |

| 4S12832 |                                                                                                                 |      |

| 4S1288  | SRAM MODULE .                                                                                                   |      |

| 4S6416  |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

| 52C9010 |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 |      |

| 56C0816 |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 | •••• |

| 56C3816 | and a second many second se | •••  |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

|         |                                                                                                                 |      |

| 5C1189  | SRAM .                                                                                                          | •••  |

| 5C1601  | SRAM .                                                                                                          |      |

| 5C1604  | SRAM .                                                                                                          |      |

| 5C1605  | SRAM .                                                                                                          | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

| 5C1608  |                                                                                                                 | •••  |

|         |                                                                                                                 |      |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••• |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••• |

|         |                                                                                                                 | •••  |

|         |                                                                                                                 | •••• |

|         |                                                                                                                 | •••• |

| 5C6404  | SRAM .                                                                                                          | •••  |

|         |                                                                                                                 |      |

|       | 3-9   |

|-------|-------|

|       | 3-41  |

|       | 3-1   |

|       | 3-17  |

|       | 5-1   |

|       | 5-13  |

|       | 5-29  |

|       | 5-41  |

|       | 5-57  |

|       | 5-69  |

| ····· | 4-1   |

|       | 4-39  |

|       | 4-51  |

|       | 4-13  |

|       | 4-61  |

|       | 2-1   |

|       | 2-11  |

|       | 2-21  |

|       | 1-25  |

|       | 1-97  |

|       | 1-133 |

|       | 1-141 |

|       | 1-161 |

|       | 1-1   |

|       | 1-33  |

|       | 1-41  |

|       | 1-49  |

|       | 1-49  |

|       | 1-109 |

|       | 4-25  |

|       | 1-17  |

|       | 1-81  |

|       | 1-89  |

|       | 1-125 |

|       | 4-73  |

|       | 1-153 |

|       | 1-105 |

|       | 1-149 |

|       | 1-107 |

|       | 1-151 |

|       | 1-169 |

|       | 1-9   |

|       | 1-57  |

|       |       |

# NUMERICAL INDEX (Continued) Part #

### PAGE

| $fall \pi$ |             |

|------------|-------------|

| 5C6405     | SRAM        |

| 5C6406     | SRAM        |

| 5C6407     | SRAM        |

| 5C6408     | SRAM        |

| 8S1632     | SRAM MODULE |

| 8\$25632   | SRAM MODULE |

| 8S6432     | SRAM MODULE |

|            |             |

| ана стана стана<br>Стана стана стан | 1-65 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                     | 3-49 |

|                                                                                                                                                                                                                                     | 3-33 |

|                                                                                                                                                                                                                                     |      |

# SRAM PRODUCT SELECTION GUIDE\*

| Memory        | Control                    | Part     | Access    | Package and Number of Pins |     |                                                                                                                 |                            |         |       |

|---------------|----------------------------|----------|-----------|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------|----------------------------|---------|-------|

| Configuration | Functions                  | Number   | Time (ns) | PDIP                       | SOJ | ZIP                                                                                                             | SOIC                       | Process | Page  |

| 16K x 1       | CE only                    | MT5C1601 | 8 to 35   | 20                         | 24  |                                                                                                                 |                            | CMOS    | 1-1   |

| 64K x 1       | CE only                    | MT5C6401 | 8 to 35   | 22                         | 24  |                                                                                                                 | 12 <del>.</del> 3          | CMOS    | 1-9   |

| 256K x 1      | CE only                    | MT5C2561 | 15 to 45  | 24                         | 24  | -                                                                                                               | -                          | CMOS    | 1-17  |

| 1 Meg x 1     | CE only                    | MT5C1001 | 20 to 45  | 28                         | 28  | -                                                                                                               | -                          | CMOS    | 1-25  |

| 4K x 4        | CE only                    | MT5C1604 | 8 to 35   | 20                         | 24  | -                                                                                                               |                            | CMOS    | 1-33  |

| 4K x 4        | CE & OE                    | MT5C1605 | 8 to 35   | 22                         | 24  |                                                                                                                 | -                          | CMOS    | 1-41  |

| 4K x 4        | Separate I/O               | MT5C1606 | 8 to 35   | 24                         | 24  | -                                                                                                               | -                          | CMOS    | 1-49  |

| 4K x 4        | Separate I/O, High-Z       | MT5C1607 | 8 to 35   | 24                         | 24  | 1997 <mark>-</mark> 1997                                                                                        | -                          | CMOS    | 1-49  |

| 16K x 4       | CE only                    | MT5C6404 | 8 to 35   | 22                         | 24  |                                                                                                                 | -                          | CMOS    | 1-57  |

| 16K x 4       | CE & OE                    | MT5C6405 | 8 to 35   | 24                         | 24  | angan <mark>-</mark> ang                                                                                        |                            | CMOS    | 1-65  |

| 16K x 4       | Separate I/O, CE1, CE2, OE | MT5C6406 | 8 to 35   | 28                         | 28  | -                                                                                                               | -                          | CMOS    | 1-73  |

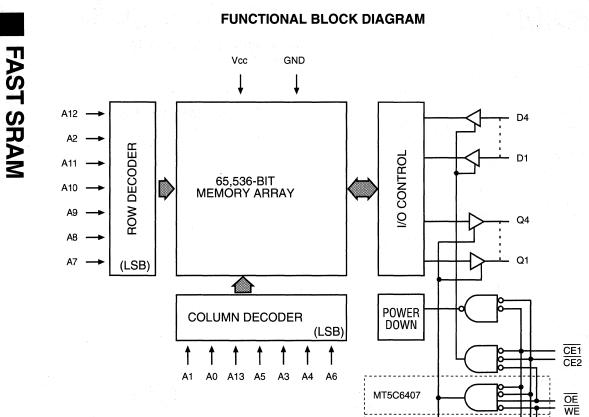

| 16K x 4       | Separate I/O, High-Z       | MT5C6407 | 8 to 35   | 28                         | 28  | -                                                                                                               |                            | CMOS    | 1-73  |

| 64K x 4       | CE only                    | MT5C2564 | 15 to 45  | 24                         | 24  | -                                                                                                               | 24                         | CMOS    | 1-81  |

| 64K x 4       | CE & OE                    | MT5C2565 | 15 to 45  | 28                         | 28  | - 1997 <mark>-</mark> 2007                                                                                      |                            | CMOS    | 1-89  |

| 256K x 4      | CE & OE                    | MT5C1005 | 20 to 45  | 28                         | 28  |                                                                                                                 | -                          | CMOS    | 1-97  |

| 1 Meg x 4     | CE & OE                    | MT5C4005 | 20 to 55  | -                          | 32  | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - | -                          | CMOS    | 1-105 |

| 1 Meg x 4     | CE & OE                    | MT5C4105 | 12 to 17  | in a te                    | 32  | -                                                                                                               |                            | CMOS    | 1-107 |

| 2K x 8        | CE & OE                    | MT5C1608 | 8 to 35   | 24                         | 24  | -                                                                                                               |                            | CMOS    | 1-109 |

| 8K x 8        | CE1, CE2 & OE              | MT5C6408 | 8 to 35   | 28                         | 28  | -                                                                                                               |                            | CMOS    | 1-117 |

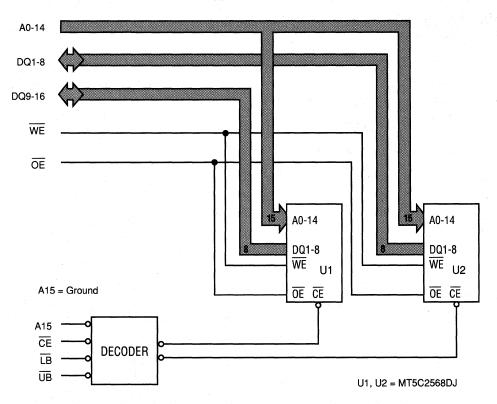

| 32K x 8       | CE & OE                    | MT5C2568 | 15 to 45  | 28                         | 28  | 28                                                                                                              | - 1911 <del>-</del> 1913 - | CMOS    | 1-125 |

| 128K x 8      | CE1, CE2 & OE              | MT5C1008 | 20 to 45  | 32                         | 32  | -                                                                                                               | -                          | CMOS    | 1-133 |

| 128K x 8      | CE & OE                    | MT5C1009 | 20 to 45  | 32                         | 32  | - 11                                                                                                            | -                          | CMOS    | 1-141 |

| 512K x 8      | CE & OE                    | MT5C4008 | 20 to 55  | -                          | 32  | -                                                                                                               | -                          | CMOS    | 1-149 |

| 512K x 8      | CE & OE                    | MT5C4108 | 12 to 17  | -                          | 36  | 1                                                                                                               |                            | CMOS    | 1-151 |

| 32K x 9       | CE1, CE2 & OE              | MT5C2889 | 15 to 25  | -                          | 32  | -                                                                                                               | -                          | CMOS    | 1-153 |

| 128K x 9      | CE & OE                    | MT5C1189 | 17 to 35  | -                          | 32  | 746 <del>-</del> 616                                                                                            |                            | CMOS    | 1-161 |

| 256K x 16     | CE & OE                    | MT5C4116 | 12 to 17  | -                          | 44  | - 1995<br>- 1995                                                                                                | 1.0                        | CMOS    | 1-169 |

\*Automotive, industrial and extended temperature specifications begin on page 1-171.

REFACE EV. 11/91

Alcron

or specifications without notice @1991, Micron Technology, Inc

right to

# SYNCHRONOUS SRAM PRODUCT SELECTION GUIDE

| Memory        | Control                                                                     | Part      | Access         | Package |      |     |         |      |

|---------------|-----------------------------------------------------------------------------|-----------|----------------|---------|------|-----|---------|------|

| Configuration | Functions                                                                   | Number    | Time (ns)      | PLCC    | PQFP | SOJ | Process | Page |

| 128K x 9      | Synchronous<br>SPARC <sup>™</sup> Cache SRAM                                | MT58C1289 | 16, 20         | · - · · | -    | 32  | CMOS    | 2-1  |

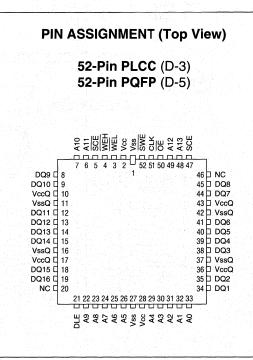

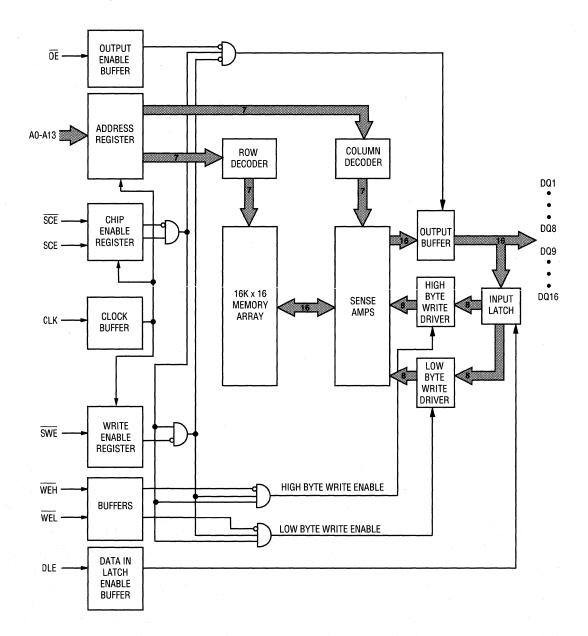

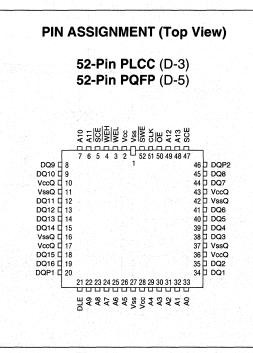

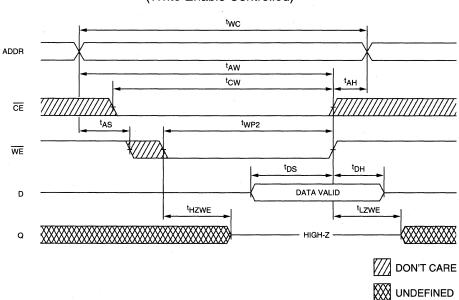

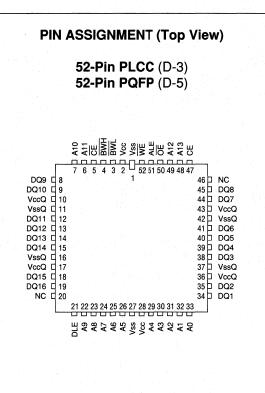

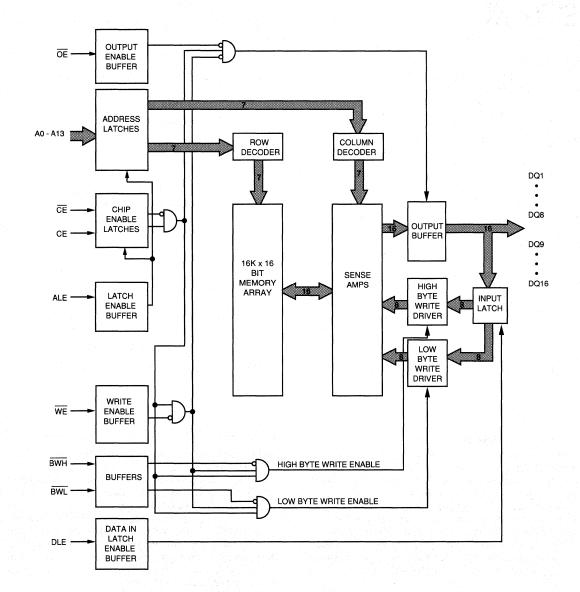

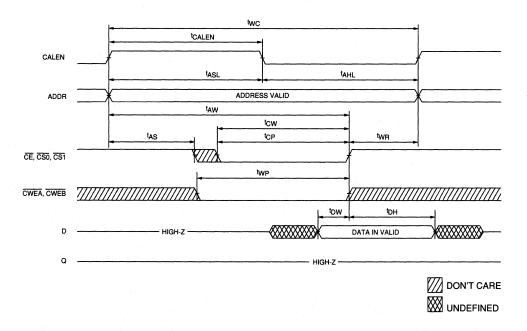

| 16K x 16      | Registered Address, Write<br>Control, Dual Chip Enable;<br>Data Input Latch | MT58C1616 | 15, 17, 20, 25 | 52      | 52   | -   | CMOS    | 2-11 |

| 16K x 18      | Registered Address, Write<br>Control, Dual Chip Enable;<br>Data Input Latch | MT58C1618 | 15, 17, 20, 25 | 52      | 52   | -   | CMOS    | 2-21 |

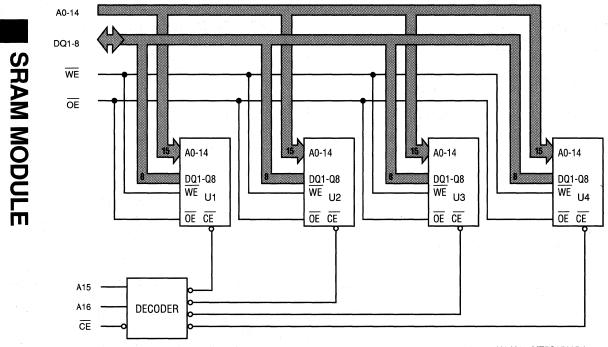

# SRAM MODULE PRODUCT SELECTION GUIDE

| Memory        | Optional     | Part      | Access                 | ccess Package and No. of Pins |     | Package and No. of Pins | Package and No. of Pins |      |  |  |

|---------------|--------------|-----------|------------------------|-------------------------------|-----|-------------------------|-------------------------|------|--|--|

| Configuration | Access Cycle | Number    | Time (ns)              | DIP                           | ZIP | SIMM                    | Process                 | Page |  |  |

| 128K x 8      | CE & OE      | MT4S1288  | 30, 35, 45             | 32                            | -   |                         | CMOS                    | 3-1  |  |  |

| 32K x 16      | CE & OE      | MT2S3216  | 30, 35, 45             | 40                            | -   | -                       | CMOS                    | 3-9  |  |  |

| 64K x 16      | CE & OE      | MT4S6416  | 30, 35, 45             | 40                            | -   | -                       | CMOS                    | 3-17 |  |  |

| 16K x 32      | CE & OE      | MT8S1632  | 15, 20, 25, 30, 35, 45 |                               | 64  | 64                      | CMOS                    | 3-25 |  |  |

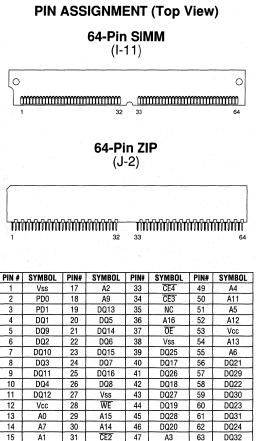

| 64K x 32      | CE & OE      | MT8S6432  | 20, 25, 30, 35, 45     | -                             | 64  | 64                      | CMOS                    | 3-33 |  |  |

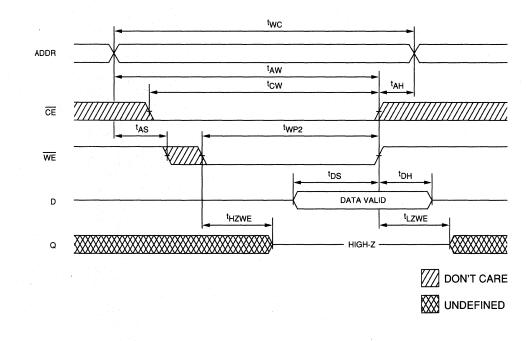

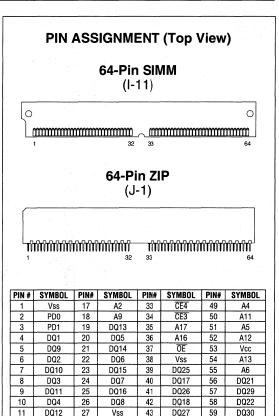

| 128K x 32     | CE & OE      | MT4S12832 | 20, 25, 35, 45         | -                             | 64  | 64                      | CMOS                    | 3-41 |  |  |

| 256K x 32     | CE & OE      | MT8S25632 | 20, 25, 35, 45         | -                             | 64  | 64                      | CMOS                    | 3-49 |  |  |

xiii

logy,

Lots or specifications without notice. ©1991, Micron Technology, Inc.

PREFACE REV. 11/91

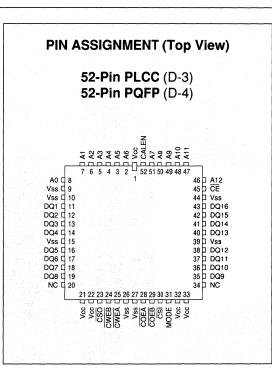

# CACHE DATA/LATCHED SRAM PRODUCT SELECTION GUIDE

| Memory                            | Control                                                             | Part      | Access         | Pac       | kage |         |      |  |

|-----------------------------------|---------------------------------------------------------------------|-----------|----------------|-----------|------|---------|------|--|

| Configuration                     | Functions                                                           | Number    | Time (ns)      | PLCC PQFP |      | Process | Page |  |

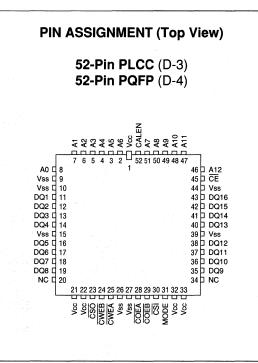

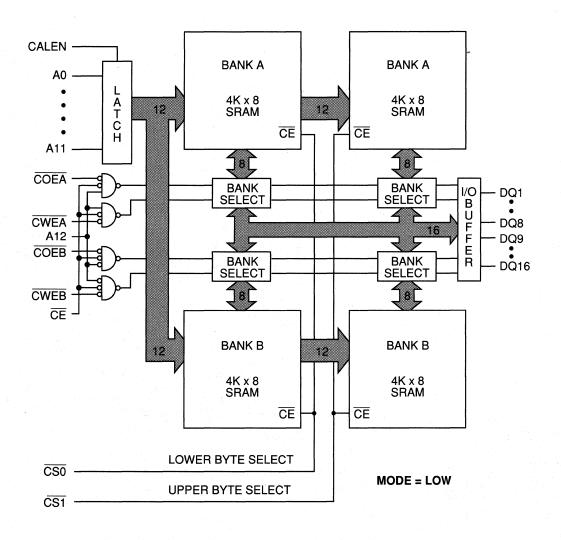

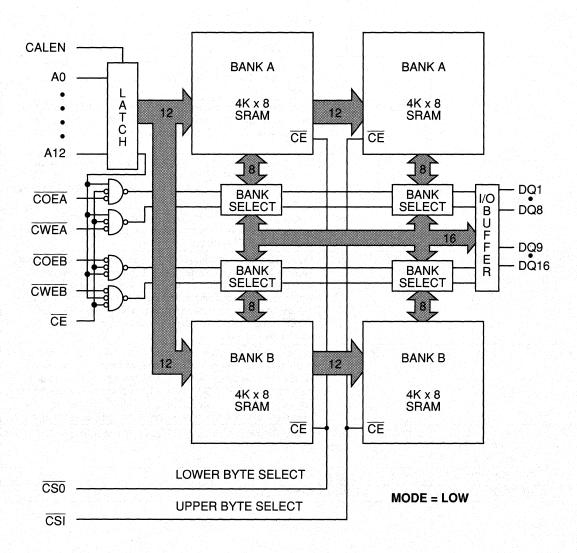

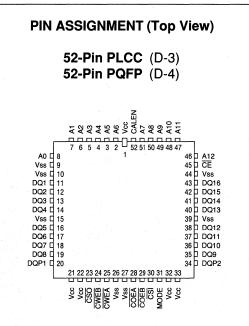

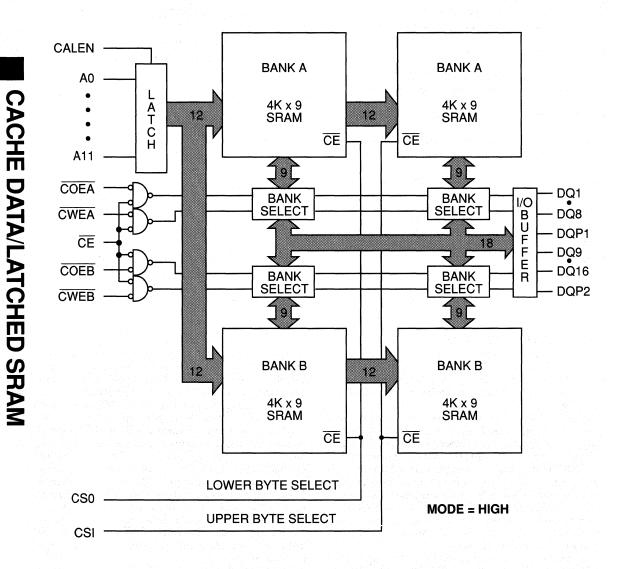

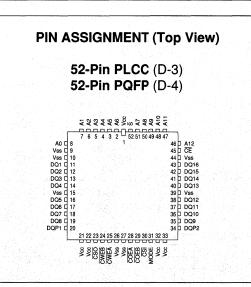

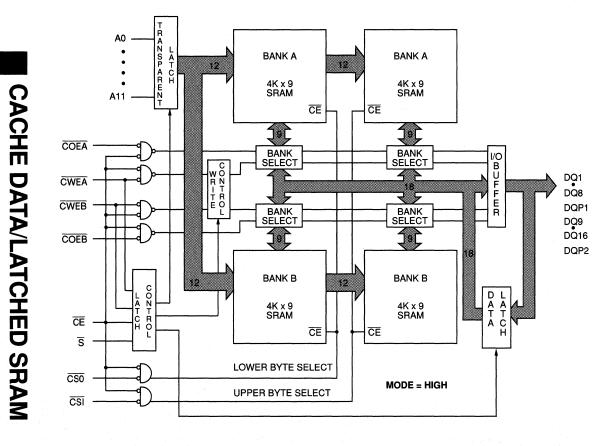

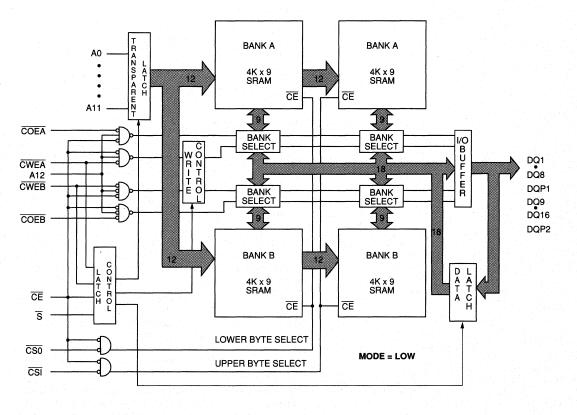

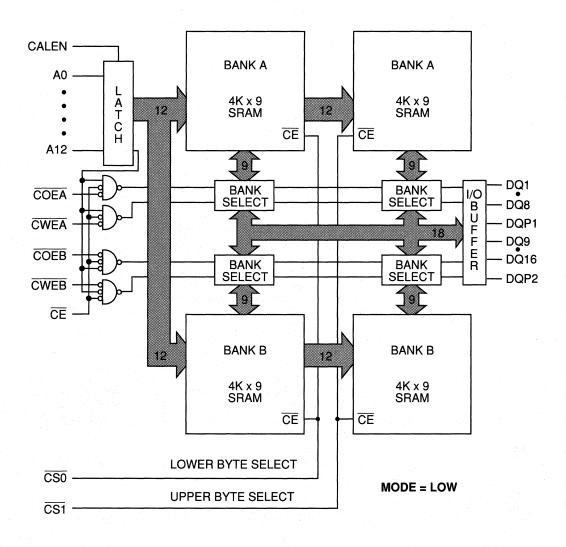

| Dual 4K x 16 or<br>Single 8K x 16 | Mode, Byte Select, CE, OE<br>Address Latch (A0-A11)                 | MT56C0816 | 20, 25, 35     | 52        | 52   | CMOS    | 4-1  |  |

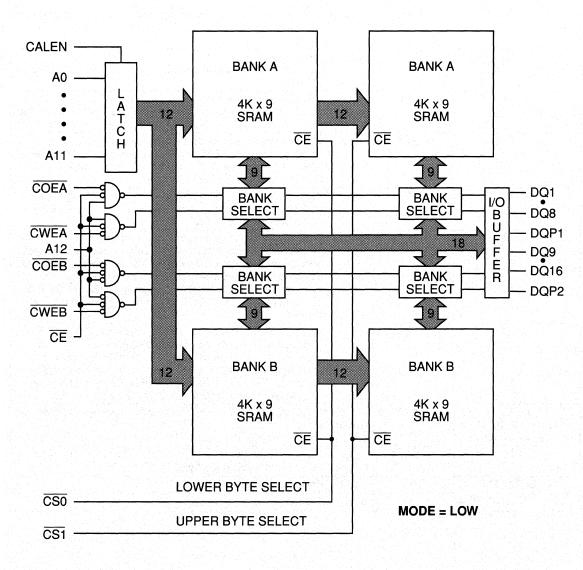

| Dual 4K x 16 or<br>Single 8K x 16 | Mode, Byte Select, CE, OE<br>Address Latch (A0-A12)                 | MT56C3816 | 20, 25, 35     | 52        | 52   | CMOS    | 4-13 |  |

| 16K x 16                          | Latched Address and Data, Dual<br>Chip Enables, Byte Write Controls | MT5C2516  | 15, 17, 20, 25 | 52        | 52   | CMOS    | 4-25 |  |

| Dual 4K x 18 or<br>Single 8K x 18 | Mode, Byte Select, CE, OE<br>Address Latch (A0-A11)                 | MT56C0818 | 20, 25, 35     | 52        | 52   | CMOS    | 4-39 |  |

| Dual 4K x 18 or<br>Single 8K x 18 | Mode, Byte Select, CE, OE<br>Synchronous Write Enable               | MT56C2818 | 24, 28         | 52        | 52   | CMOS    | 4-51 |  |

| Dual 4K x 18 or<br>Single 8K x 18 | Mode, Byte Select, CE, OE<br>Address Latch (A0-A12)                 | MT56C3818 | 20, 25, 35     | 52        | 52   | CMOS    | 4-61 |  |

| 16K x 18                          | Latched Address and Data, Dual<br>Chip Enables, Byte Write Controls | MT5C2818  | 15, 17, 20, 25 | 52        | 52   | CMOS    | 4-73 |  |

×i

cifications without notice Micron Technology, Inc

PREFACE REV. 11/91

# FIFO MEMORIES PRODUCT SELECTION GUIDE

| Memory        | Control                                         | Part      | Cycle          | Package | and Numbe | er of Pins |         | Page |  |

|---------------|-------------------------------------------------|-----------|----------------|---------|-----------|------------|---------|------|--|

| Configuration | Functions                                       | Number    | Time (ns)      | PDIP    | PLCC      | SOJ        | Process |      |  |

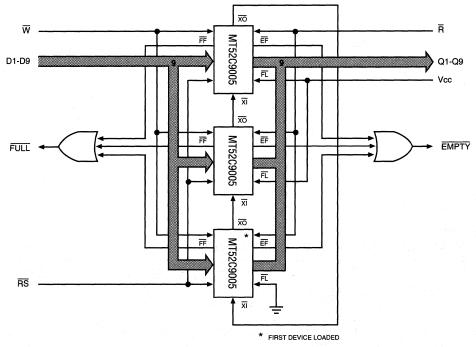

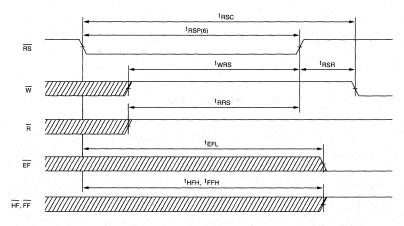

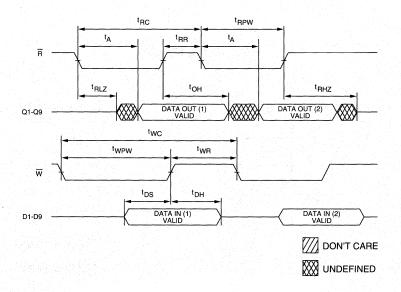

| 512 x 9       | Expandable Depth and Width                      | MT52C9005 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-1  |  |

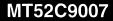

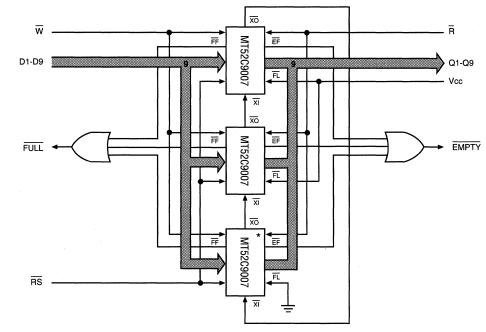

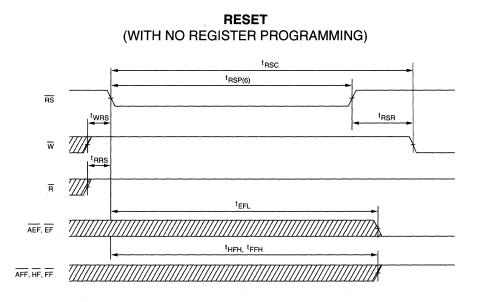

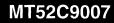

| 512 x 9       | Programmable Flag<br>Expandable Depth and Width | MT52C9007 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-13 |  |

| 1K x 9        | Expandable Depth and Width                      | MT52C9010 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-29 |  |

| 1K x 9        | Programmable Flag<br>Expandable Depth and Width | MT52C9012 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-41 |  |

| 2K x 9        | Expandable Depth and Width                      | MT52C9020 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-57 |  |

| 2K x 9        | Programmable Flag<br>Expandable Depth and Width | MT52C9022 | 15, 20, 25, 35 | 28      | 32        | 28         | CMOS    | 5-69 |  |

Micron Technology, Inc., reserves the right to charge products or specifications without notice. © 1991, Micron Technology, Inc.

≳

PREFACE REV. 11/91

# **APPLICATION/TECHNICAL NOTE SELECTION GUIDE**

| Application/Technical Note | Title                                     | Page |

|----------------------------|-------------------------------------------|------|

| TN-00-01                   | Moisture Absorption in Plastic Packages   | 6-1  |

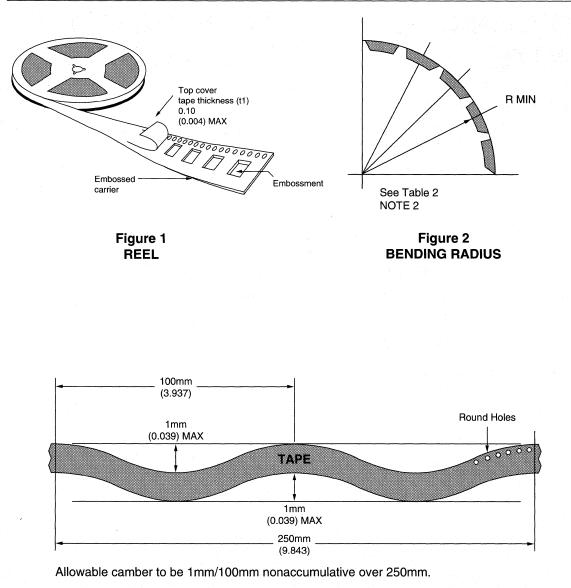

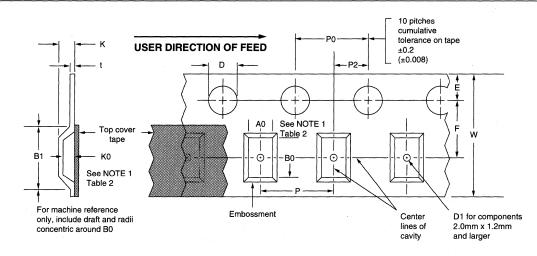

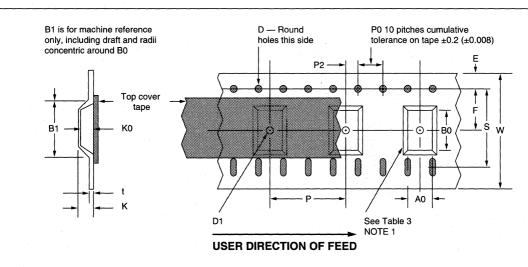

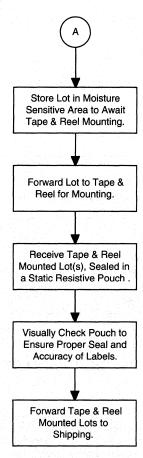

| TN-00-02                   | Micron Tape and Reel Procedures           | 6-3  |

| TN-05-02                   | SRAM Bus Contention Design Considerations | 6-9  |

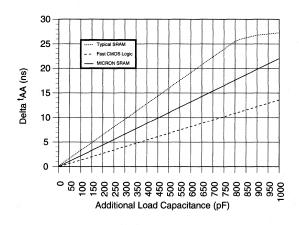

| TN-05-03                   | SRAM Capacitive Loading                   | 6-13 |

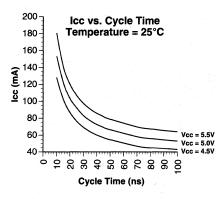

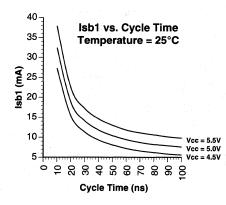

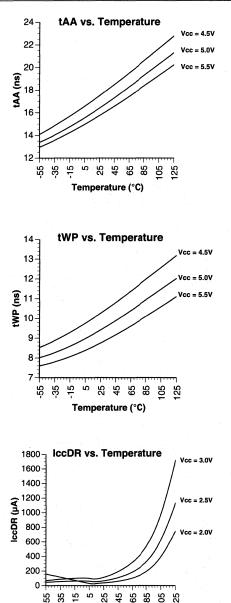

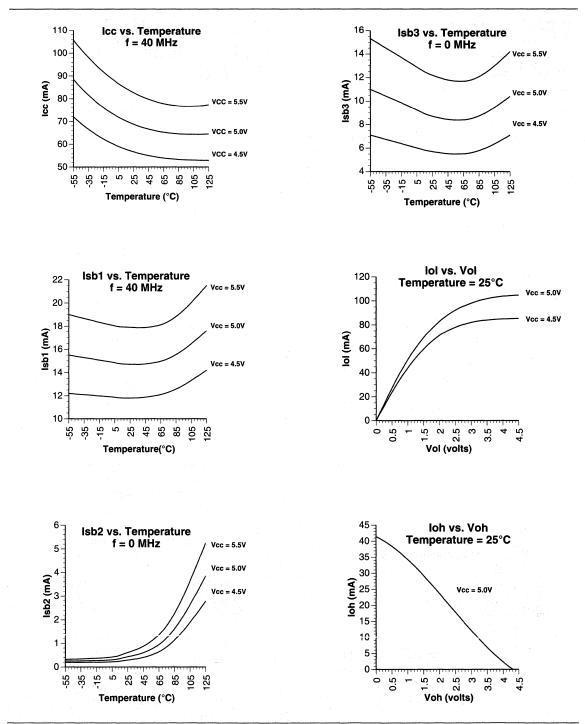

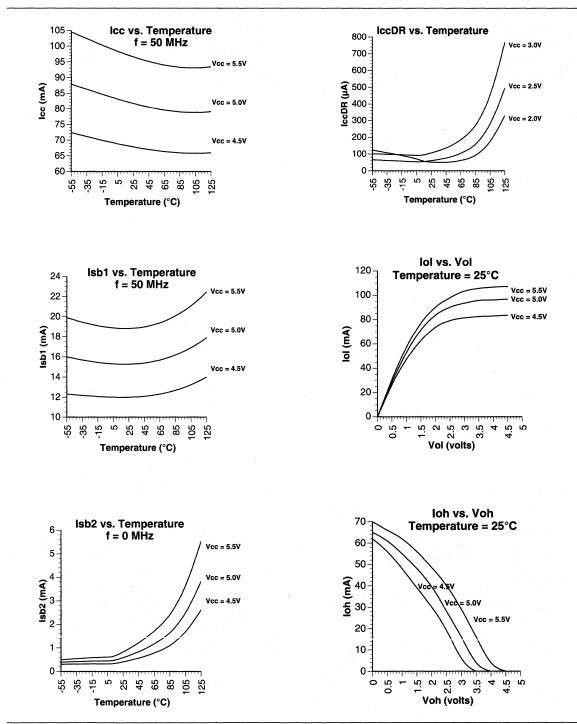

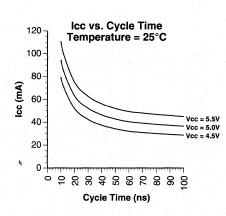

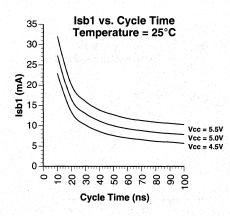

| TN-05-06                   | 1 Meg Fast SRAM Typical Operating Curves  | 6-15 |

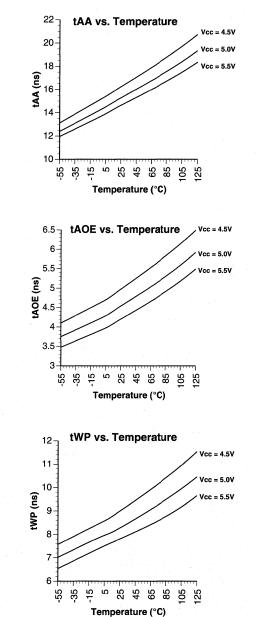

| TN-05-07                   | 256K Fast SRAM Typical Operating Curves   | 6-17 |

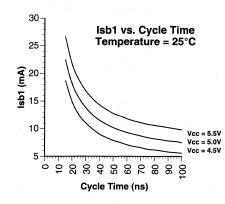

| TN-05-08                   | 64K Fast SRAM Typical Operating Curves    | 6-19 |

| TN-05-12                   | 128K x 8 SRAM Chip Enable Options         | 6-21 |

| AN-56-01                   | MT56C0816 Cache Data SRAM Family          | 6-23 |

ž

© 1991, Micron Technology, Inc.

#

| STATIC RAMS                 | 1 |

|-----------------------------|---|

| SYNCHRONOUS SRAMS           | 2 |

| SRAM MODULES                | 3 |

| CACHE DATA/LATCHED SRAMS    | 4 |

| FIFO MEMORIES               | 5 |

| APPLICATION/TECHNICAL NOTES | 6 |

| PRODUCT RELIABILITY         | 7 |

| PACKAGE INFORMATION         | 8 |

| SALES INFORMATION           | 9 |

### **SRAM PRODUCT SELECTION GUIDE\***

| Memory Control |                            | Part     | Access    | Pa   | ckage and l | Number of | Pins |         |       |

|----------------|----------------------------|----------|-----------|------|-------------|-----------|------|---------|-------|

| Configuration  | Functions                  | Number   | Time (ns) | PDIP | SOJ         | ZIP       | SOIC | Process | Page  |

| 16K x 1        | CE only                    | MT5C1601 | 8 to 35   | 20   | 24          | -         |      | CMOS    | 1-1   |

| 64K x 1        | CE only                    | MT5C6401 | 8 to 35   | 22   | 24          | -         | -    | CMOS    | 1-9   |

| 256K x 1       | CE only                    | MT5C2561 | 15 to 45  | 24   | 24          |           | -    | CMOS    | 1-17  |

| 1 Meg x 1      | CE only                    | MT5C1001 | 20 to 45  | 28   | 28          | -         | -    | CMOS    | 1-25  |

| 4K x 4         | CE only                    | MT5C1604 | 8 to 35   | 20   | 24          | -         | -    | CMOS    | 1-33  |

| 4K x 4         | CE & OE                    | MT5C1605 | 8 to 35   | 22   | 24          | -         | -    | CMOS    | 1-41  |

| 4K x 4         | Separate I/O               | MT5C1606 | 8 to 35   | 24   | 24          | -         | -    | CMOS    | 1-49  |

| 4K x 4         | Separate I/O, High-Z       | MT5C1607 | 8 to 35   | 24   | 24          | -         | -    | CMOS    | 1-49  |

| 16K x 4        | CE only                    | MT5C6404 | 8 to 35   | 22   | 24          |           | -    | CMOS    | 1-57  |

| 16K x 4        | CE & OE                    | MT5C6405 | 8 to 35   | 24   | 24          | -         | -    | CMOS    | 1-65  |

| 16K x 4        | Separate I/O, CE1, CE2, OE | MT5C6406 | 8 to 35   | 28   | 28          | -         | - '  | CMOS    | 1-73  |

| 16K x 4        | Separate I/O, High-Z       | MT5C6407 | 8 to 35   | 28   | 28          | -         | - ** | CMOS    | 1-73  |

| 64K x 4        | CE only                    | MT5C2564 | 15 to 45  | 24   | 24          | -         | 24   | CMOS    | 1-81  |

| 64K x 4        | CE & OE                    | MT5C2565 | 15 to 45  | 28   | 28          | -         | -    | CMOS    | 1-89  |

| 256K x 4       | CE & OE                    | MT5C1005 | 20 to 45  | 28   | 28          | · · ·     | - 1  | CMOS    | 1-97  |

| 1 Meg x 4      | CE & OE                    | MT5C4005 | 20 to 55  | -    | 32          | -         | -    | CMOS    | 1-105 |

| 1 Meg x 4      | CE & OE                    | MT5C4105 | 12 to 17  |      | 32          |           | -    | CMOS    | 1-107 |

| 2K x 8         | CE & OE                    | MT5C1608 | 8 to 35   | 24   | 24          | -         | -    | CMOS    | 1-109 |

| 8K x 8         | CE1, CE2 & OE              | MT5C6408 | 8 to 35   | 28   | 28          | -         | -    | CMOS    | 1-117 |

| 32K x 8        | CE & OE                    | MT5C2568 | 15 to 45  | 28   | 28          | 28        | -    | CMOS    | 1-125 |

| 128K x 8       | CE1, CE2 & OE              | MT5C1008 | 20 to 45  | 32   | 32          | -         |      | CMOS    | 1-133 |

| 128K x 8       | CE & OE                    | MT5C1009 | 20 to 45  | 32   | 32          | -         | -    | CMOS    | 1-141 |

| 512K x 8       | CE & OE                    | MT5C4008 | 20 to 55  | -    | 32          | -"        |      | CMOS    | 1-149 |

| 512K x 8       | CE & OE                    | MT5C4108 | 12 to 17  | -    | 36          | -         |      | CMOS    | 1-151 |

| 32K x 9        | CE1, CE2 & OE              | MT5C2889 | 15 to 25  | -    | 32          | -         | -    | CMOS    | 1-153 |

| 128K x 9       | CE & OE                    | MT5C1189 | 17 to 35  | -    | 32          | -         | -    | CMOS    | 1-161 |

| 256K x 16      | CE & OE                    | MT5C4116 | 12 to 17  | -    | 44          | -         | -    | CMOS    | 1-169 |

\*Automotive, industrial and extended temperature specifications begin on page 1-171. NOTE: Many Micron components are available in bare die form. Contact Micron Technology, Inc., for more information.

ICTECHNOLOGY.INC.

### MT5C1601

FAST SRAM

# SRAM

# 16K x 1 SRAM

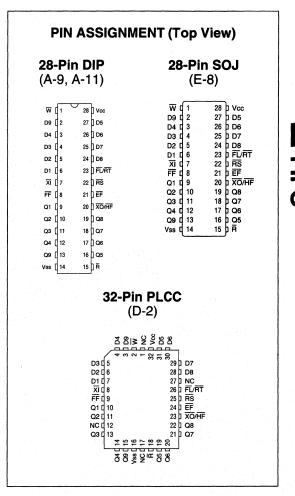

| <b>EATURES</b><br>High speed: 8, 10, 12, 15, 20, 25 ar |                                                                         | PIN ASSIGNMENT (Top View)                              |

|--------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|

| High-performance, low-power, C                         | MOS double-metal                                                        |                                                        |

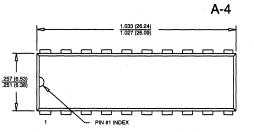

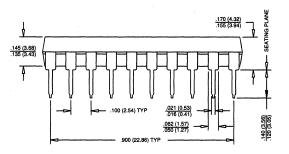

| process                                                |                                                                         | 20-Pin DIP                                             |

| Single +5V $\pm 10\%$ power supply                     |                                                                         | (A-4)                                                  |

| Easy memory expansion with CE                          | option                                                                  |                                                        |

| All inputs and outputs are TTL co                      | ompatible                                                               |                                                        |

| OPTIONS M                                              | ARKING                                                                  | A1 [ 2 19 ] A13                                        |

| Timing                                                 |                                                                         | A2 [] 3 18 [] A12                                      |

| 8ns access (preliminary)                               | - 8                                                                     | A3 🛛 4 17 🗍 A11                                        |

| 10ns access                                            | -10                                                                     | [1] 그는 영양과 같은 것 같아.] 여름 가슴 다.[편집]은 일 수영을 다.            |

| 12ns access                                            | -12                                                                     | A4 [] 5 16 [] A10                                      |

| 15ns access                                            | -15                                                                     | A5 [] 6 15 ]] A9                                       |

| 20ns access                                            | -20                                                                     | A6 🛛 7 14 🗍 A8                                         |

| 25ns access                                            | -25                                                                     | [ - 영화 영상 등 등 전 - 영상 이 및 전 1 등 이상 [ 영상 등 등 등 이 등 이 가격을 |

| 35ns access                                            | -35                                                                     | Q [] 8 13 [] A7                                        |

| Packages                                               |                                                                         | WE [] 9 12 ]] D                                        |

| Plastic DIP (300 mil)                                  | None                                                                    | Vss [ 10 11 ] CE                                       |

| Plastic SOJ (300 mil)                                  | DI                                                                      |                                                        |

| Available in ceramic packages tes                      |                                                                         |                                                        |

| specifications. Please refer to Mic                    |                                                                         | 24-Pin SOJ                                             |

| Book.                                                  |                                                                         | (E-4)                                                  |

| 2V data retention                                      |                                                                         | A0 [ 1 24 ] Vcc                                        |

|                                                        | 가락 전 이미 이 것은 것은 것이 있을까? 이 것이다.<br>같은 것은 것이 같은 것이 있는 것이 있는 것이 같이 있는 것이다. | A1 [ 2 23 ] A13                                        |

| Temperature                                            |                                                                         | A2 [] 3 22 [] A12<br>A3 [] 4 21 [] A11                 |

| Industrial $(-40^{\circ}C \text{ to } +85^{\circ}C)$   | IT                                                                      | A3 L 4 21 L A11<br>A4 L 5 20 L A10                     |

| Automotive $(-40^{\circ}C \text{ to } +125^{\circ}C)$  | AT                                                                      | NC 🛛 6 19 🗍 NC                                         |

| Extended (-55°C to +125°C)                             | XT                                                                      |                                                        |

|                                                        |                                                                         | A5 [] 8 17 [] A9<br>A6 [] 9 16 [] A8                   |

|                                                        | · · · · · · · · · · · · · · · · · · ·                                   |                                                        |

|                                                        |                                                                         | WE [ 11 14 ] <u>D</u>                                  |

|                                                        | 수는 것이 많은 것 것은 것이 같아.                                                    | Vss [ 12 13 ] ¯Ē                                       |

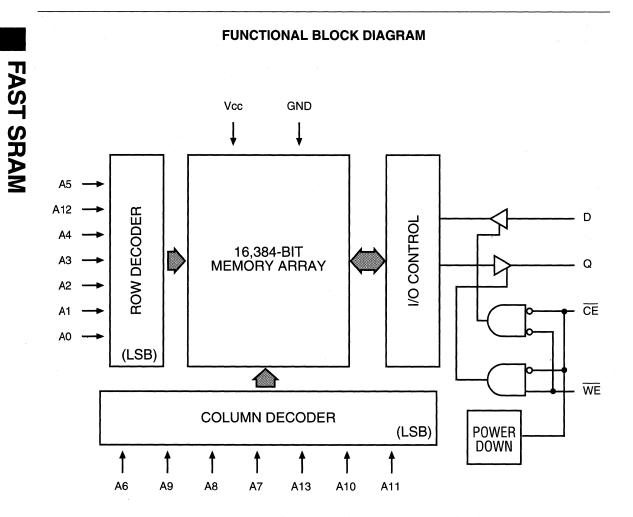

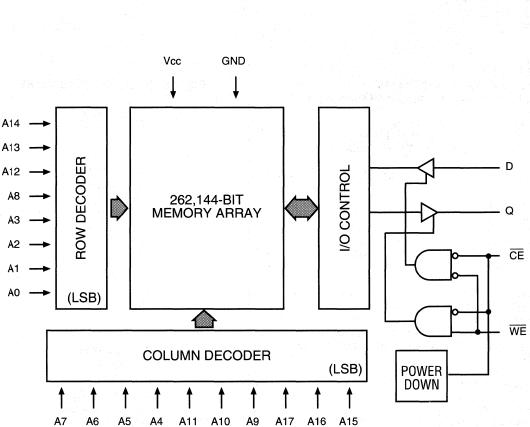

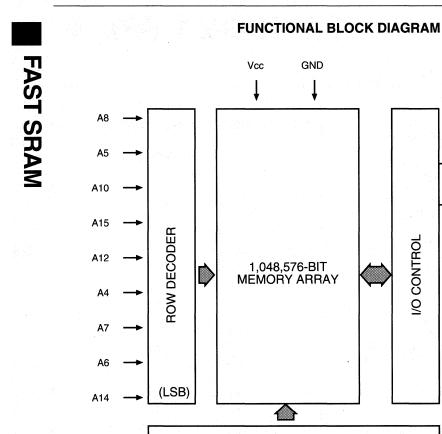

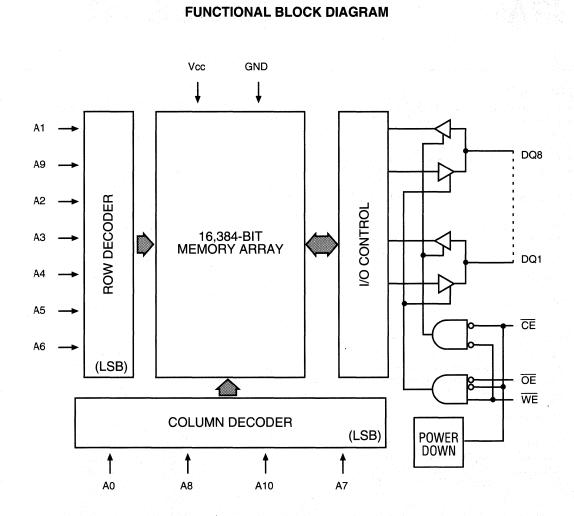

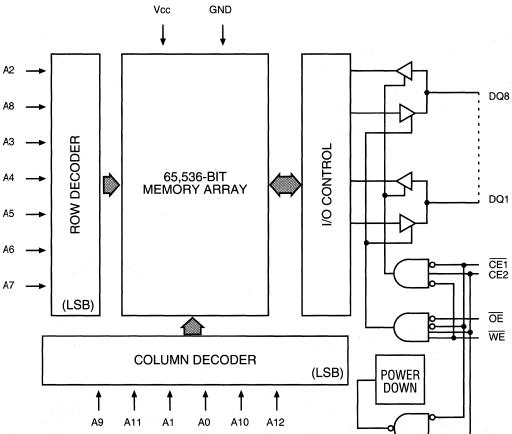

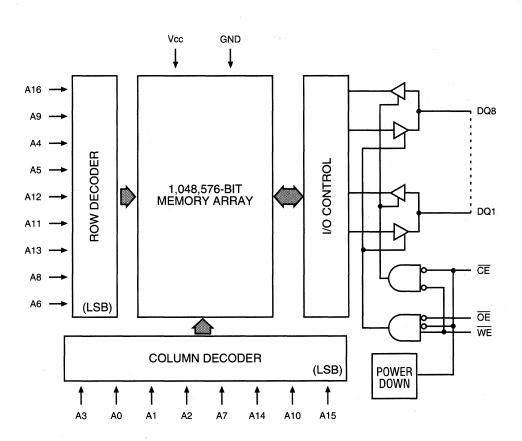

### **GENERAL DESCRIPTION**

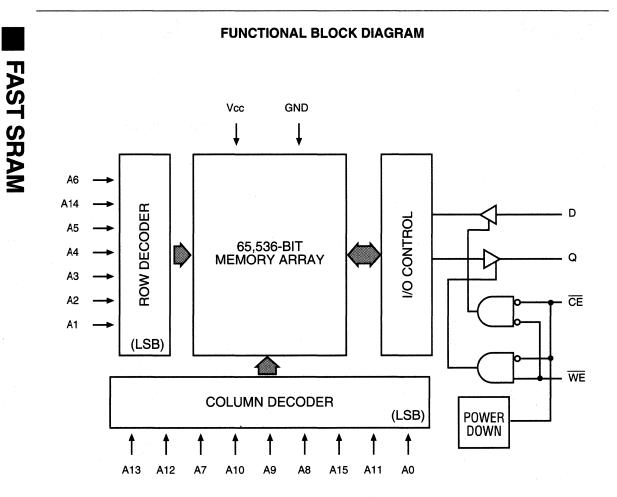

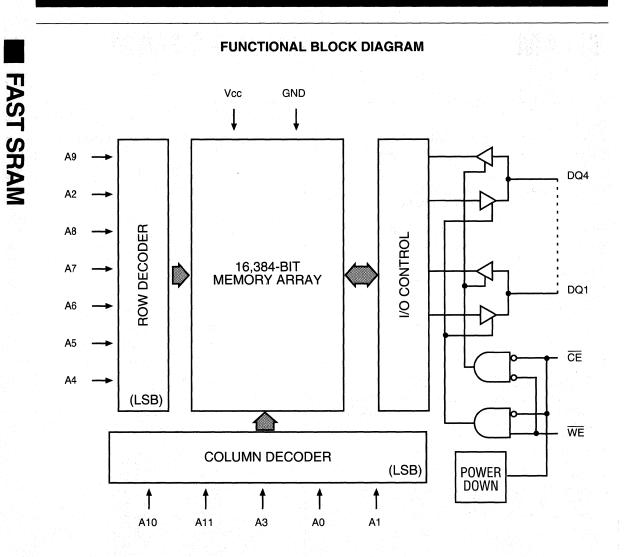

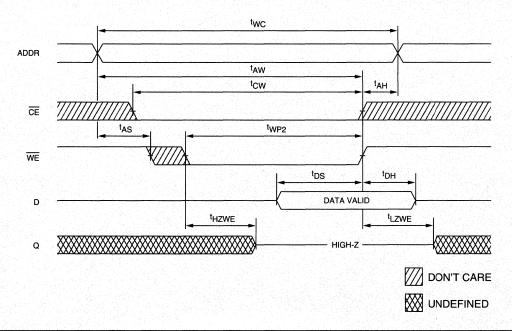

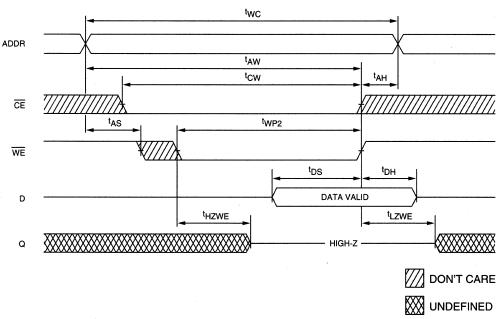

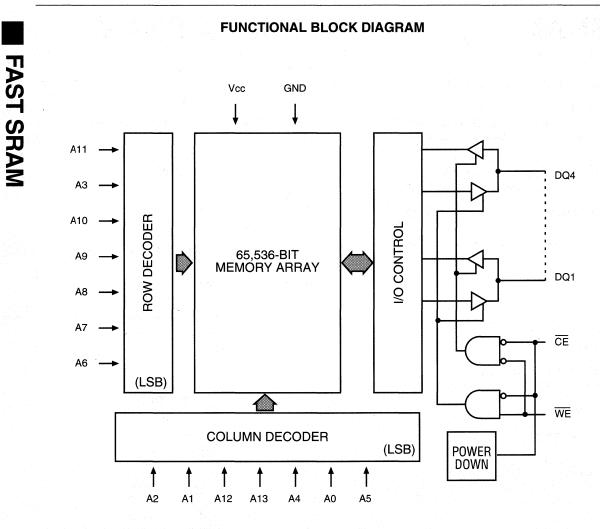

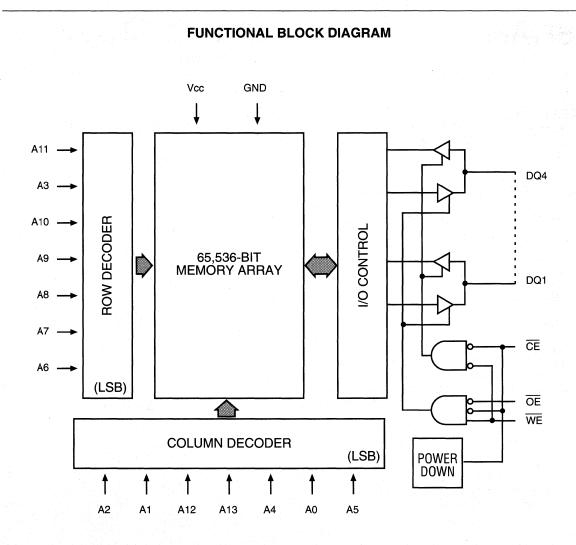

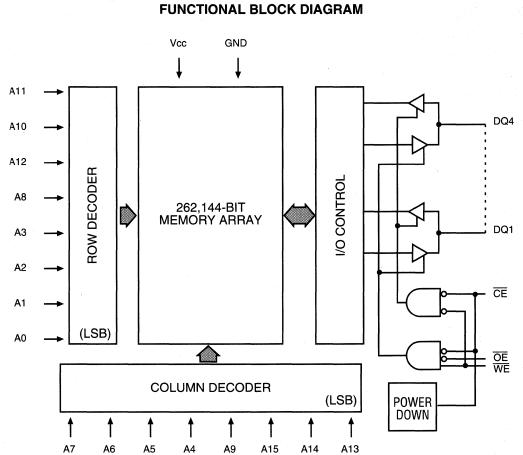

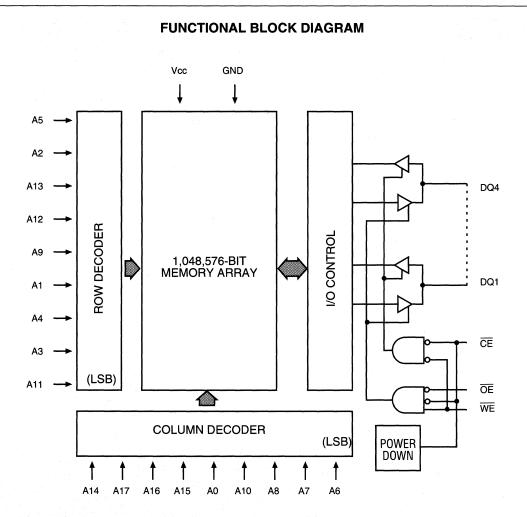

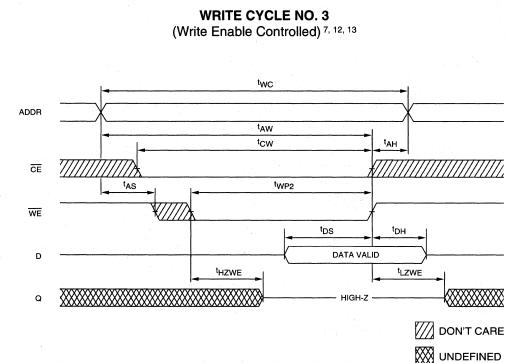

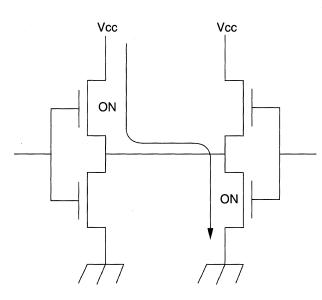

The Micron SRAM family employs high-speed, lowoower CMOS designs using a four-transistor memory cell. Micron SRAMs are fabricated using double-layer metal, louble-layer polysilicon technology.

For flexibility in high-speed memory applications, Micron offers chip enable  $\overline{(CE)}$  on all organizations. This enhancement can place the outputs in High-Z for additional lexibility in system design. The x1 configuration features reparate data input and output.

Writing to these devices is accomplished when write enable (WE) and  $\overline{CE}$  inputs are both LOW. Reading is accomplished when WE remains HIGH and  $\overline{CE}$  goes to LOW. The device offers a reduced power standby mode when disabled. This allows system designers to achieve their low standby power requirements.

All devices operate from a single +5V power supply and all inputs and outputs are fully TTL compatible.

MT5C1601

### **TRUTH TABLE**

| MODE    | CE | WE | OUTPUT | POWER   |

|---------|----|----|--------|---------|

| STANDBY | н  | X  | HIGH-Z | STANDBY |

| READ    | L  | Н  | Q      | ACTIVE  |

| WRITE   | L  | L  | HIGH-Z | ACTIVE  |

1-2

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply Relative to Vss1V to +7V |

|------------------------------------------------|

| Storage Temperature (Plastic)                  |

| Power Dissipation                              |

| Short Circuit Output Current                   |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS (0°C $\leq T_{A} \leq 70$ °C; Vcc = 5V $\pm 10$ %)

| DESCRIPTION                  | CONDITIONS                            | SYMBOL | MIN  | MAX    | UNITS | NOTES |

|------------------------------|---------------------------------------|--------|------|--------|-------|-------|

| Input High (Logic 1) Voltage |                                       | Vін    | 2.2  | Vcc +1 | V     | 1     |

| Input Low (Logic 0) Voltage  |                                       | VIL    | -0.5 | 0.8    | V     | 1, 2  |

| Input Leakage Current        | $0V \le V_{IN} \le V_{CC}$            | ILi    | -5   | 5      | μA    |       |

| Output Leakage Current       | Output(s) Disabled<br>0V ≤ Vou⊤ ≤ Vcc | ILo    | -5   | 5      | μA    |       |

| Output High Voltage          | lон = -4.0mA                          | Vон    | 2.4  |        | V     | 1     |

| Output Low Voltage           | IoL = 8.0mA                           | Vol    |      | 0.4    | V     | 1     |

|                                    |                                                                                                                                                                                                             |        |     |     | MAX |     |     |     |     |     |       |       |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|--|--|

| DESCRIPTION                        | CONDITIONS                                                                                                                                                                                                  | SYMBOL | ТҮР | -8  | -10 | -12 | -15 | -20 | -25 | -35 | UNITS | NOTES |  |  |

| Power Supply<br>Current: Operating | CE ≤ VIL; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>Outputs Open                                                                                                                                         | lcc    | 65  | 160 | 150 | 140 | 120 | 110 | 100 | 90  | mA    | 3, 14 |  |  |

| Power Supply<br>Current: Standby   | CE ≥ VIH; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>Outputs Open                                                                                                                                         | ISB1   | 20  | 55  | 50  | 45  | 40  | 35  | 30  | 25  | mA    | 14    |  |  |

|                                    | $\label{eq:cell} \begin{split} \overline{CE} \geq & \text{Vcc -0.2V; Vcc} = \text{MAX} \\ & \text{ViL} \leq & \text{Vss} + 0.2\text{V} \\ & \text{ViH} \geq & \text{Vcc} - 0.2\text{V; } f = 0 \end{split}$ | ISB2   | 0.4 | 3   | 3   | 3   | 3   | 3   | 3   | 3   | mA    | 14    |  |  |

### CAPACITANCE

| DESCRIPTION        | CONDITIONS                       | SYMBOL | MAX | UNITS | NOTES |

|--------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C, f = 1 MHz | С      | 7   | pF    | 4     |

| Output Capacitance | Vcc = 5V                         | Co     | 7.  | pF    | 4     |

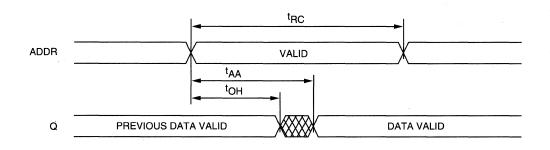

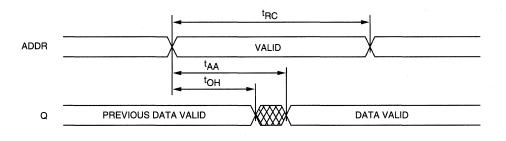

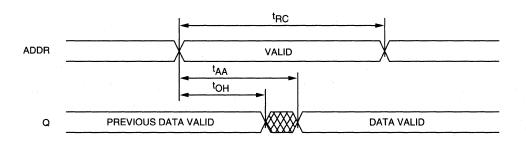

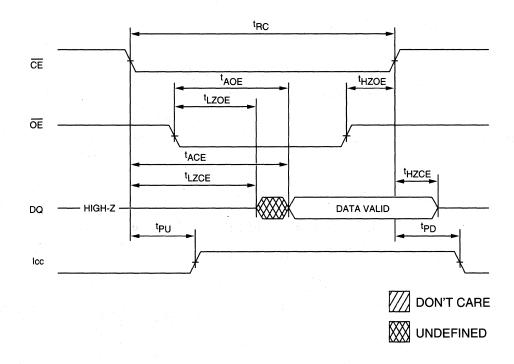

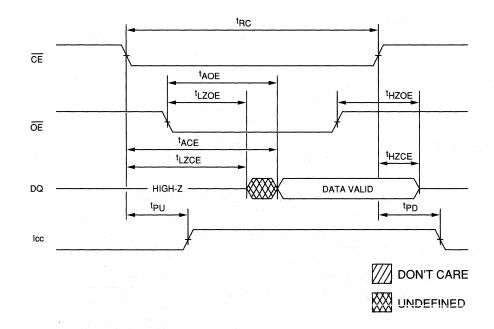

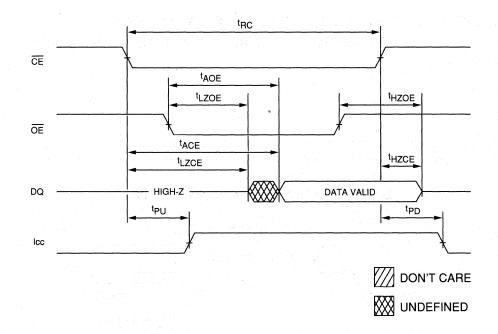

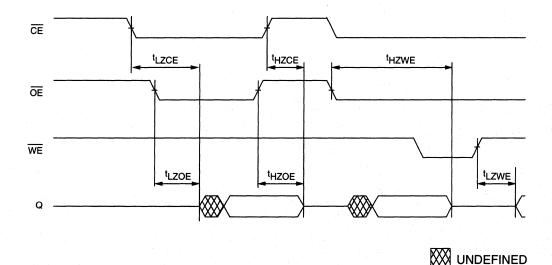

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Note 5, 13) ( $0^{\circ}C \le T_{A} \le 70^{\circ}C$ ; Vcc = 5V ±10%)

| DESCRIPTION                      |                   | -8* |          | -10      |      | -12 |          | -15 |     | -20             |     | -25 |     | -35 |          |       |                             |

|----------------------------------|-------------------|-----|----------|----------|------|-----|----------|-----|-----|-----------------|-----|-----|-----|-----|----------|-------|-----------------------------|

| DESCRIPTION                      | SYM               | MIN | МАХ      | MIN      | МАХ  | MIN | MAX      | MIN | MAX | MIN             | MAX | MIN | MAX | MIN | MAX      | UNITS | NOTES                       |

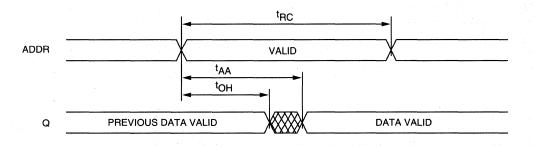

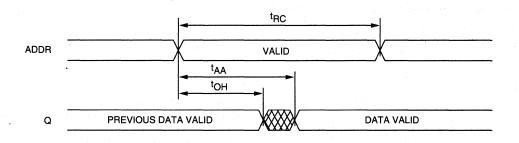

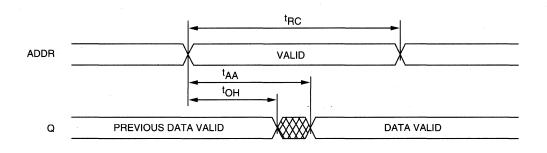

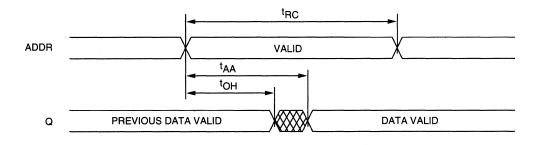

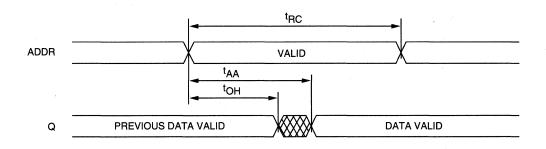

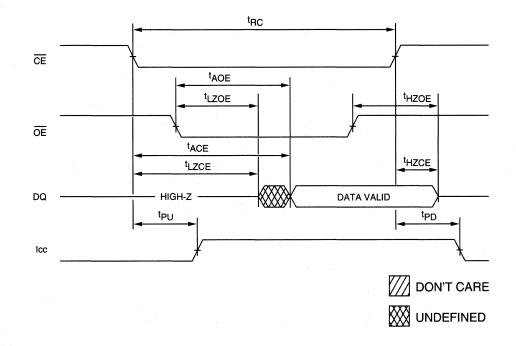

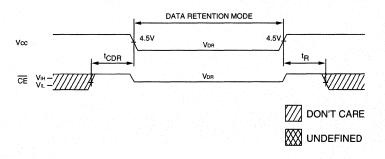

| READ Cycle                       |                   |     | <b>.</b> | <b>.</b> |      |     | <b>.</b> |     |     |                 |     |     | •   |     | <b>.</b> | J     | <b>1</b>                    |

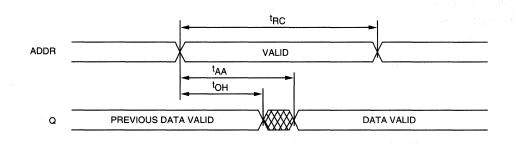

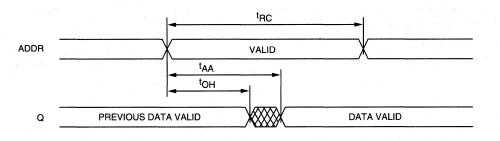

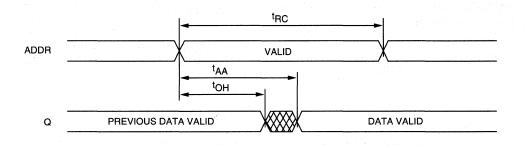

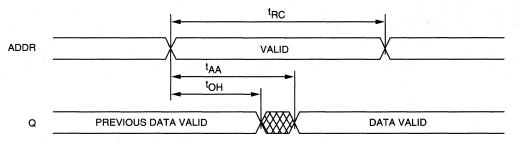

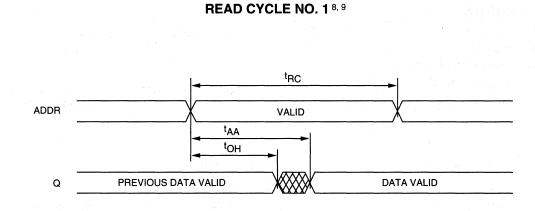

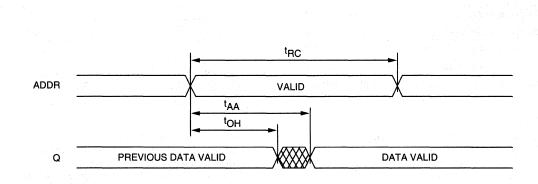

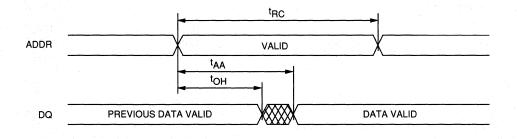

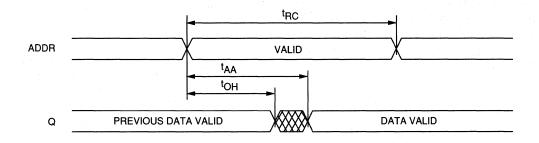

| READ cycle time                  | <sup>t</sup> RC   | 8   |          | 10       |      | 12  |          | 15  |     | 20              |     | 25  |     | 35  |          | ns    |                             |

| Address access time              | tAA               |     | 8        |          | 10   |     | 12       |     | 15  | in the<br>State | 20  |     | 25  |     | 35       | ns    |                             |

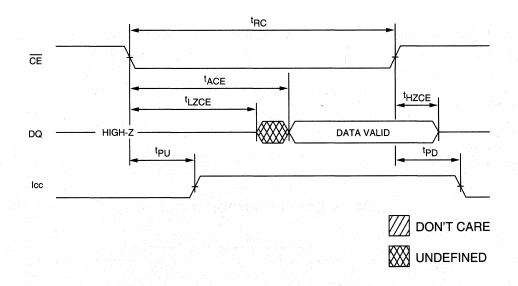

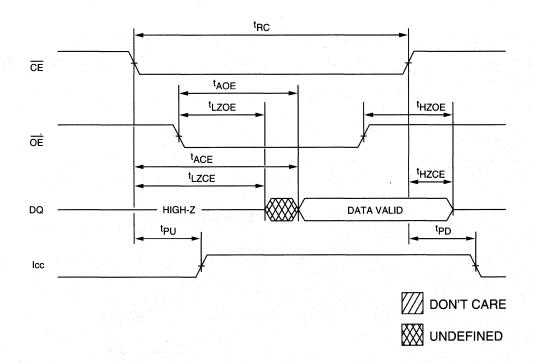

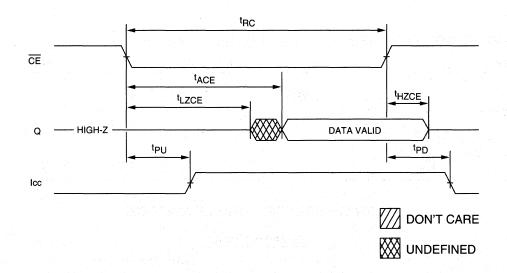

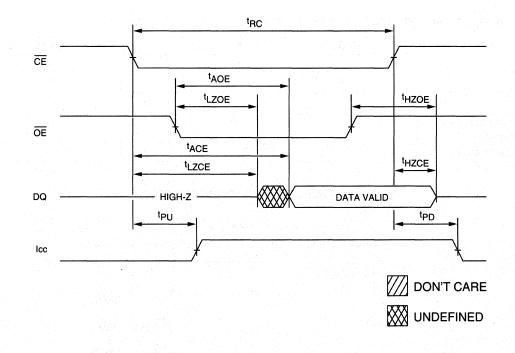

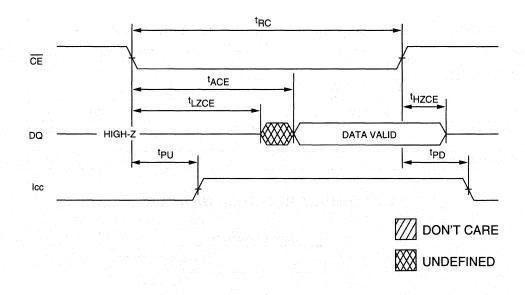

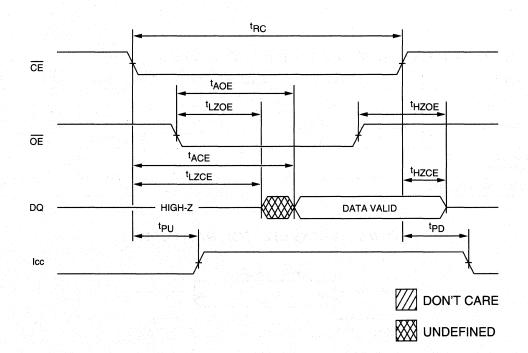

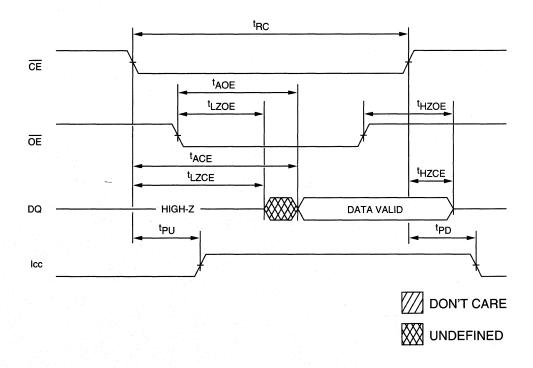

| Chip Enable access time          | <sup>t</sup> ACE  |     | 7        |          | 9    |     | 10       |     | 12  |                 | 15  |     | 20  |     | 30       | ns    |                             |

| Output hold from address change  | tОН               | 3   |          | 3        |      | 3   | 1        | 3   |     | 3               |     | 3   |     | 3   |          | ns    | A COR<br>Service<br>Service |

| Chip Enable to output in Low-Z   | <sup>t</sup> LZCE | 2   |          | 2        |      | 2   |          | 3   |     | 5               |     | 5   |     | 5   |          | ns    |                             |

| Chip disable to output in High-Z | <sup>t</sup> HZCE |     | 4        |          | 5    |     | 6        |     | 7   |                 | 8   |     | 8   |     | 8        | ns    | 6, 7                        |

| Chip Enable to power-up time     | <sup>t</sup> PU   | 0   |          | 0        |      | 0   |          | 0   | -   | 0               |     | 0   |     | 0   |          | ns    |                             |

| Chip disable to power-down time  | tPD               |     | 8        |          | 10   |     | 12       |     | 15  |                 | 20  |     | 25  |     | 35       | ns    | 1                           |

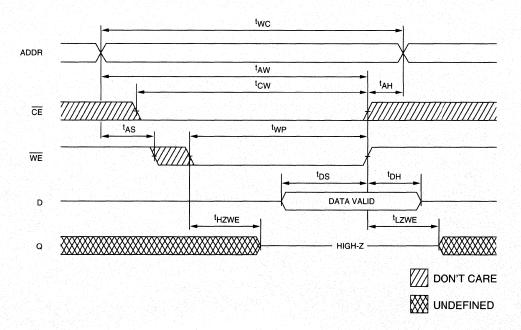

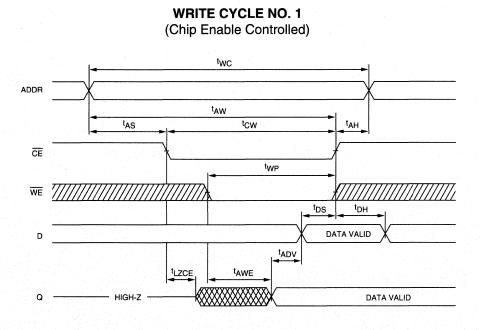

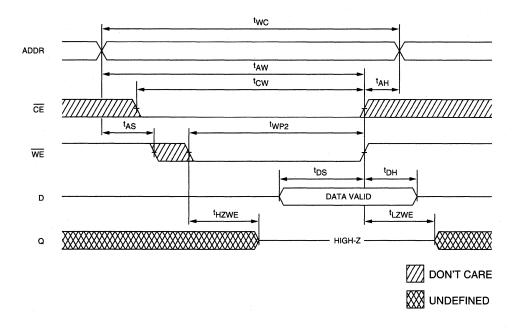

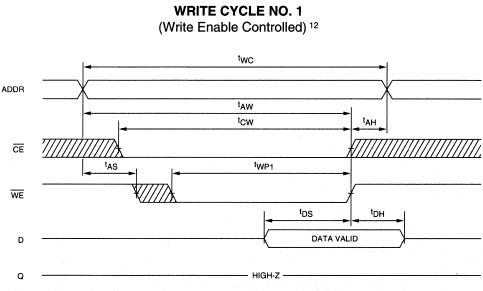

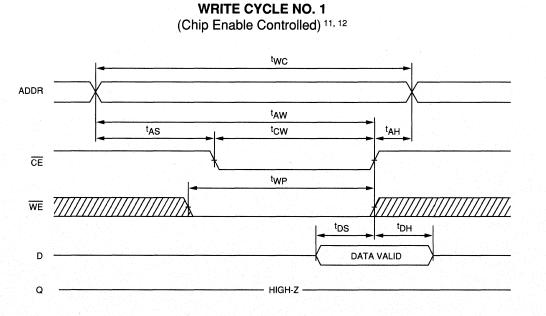

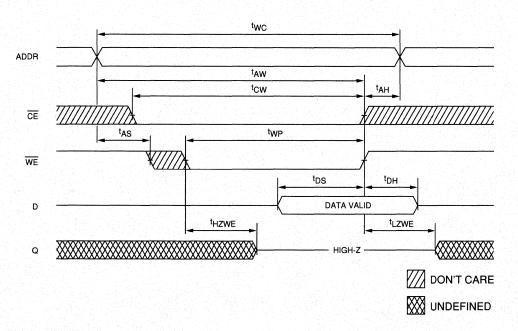

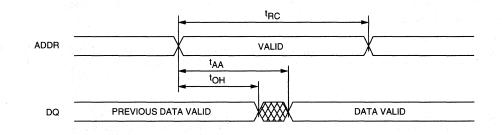

| WRITE Cycle                      |                   |     |          |          |      |     |          |     | 1   |                 |     |     |     |     |          |       |                             |

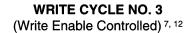

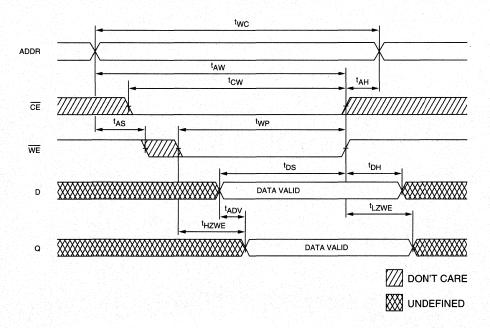

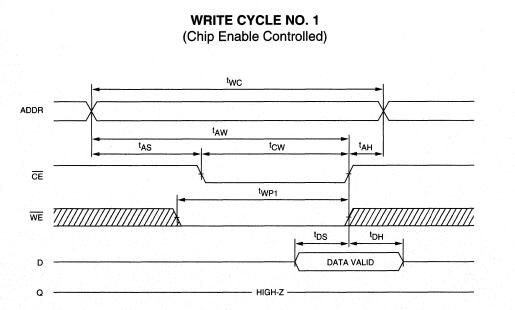

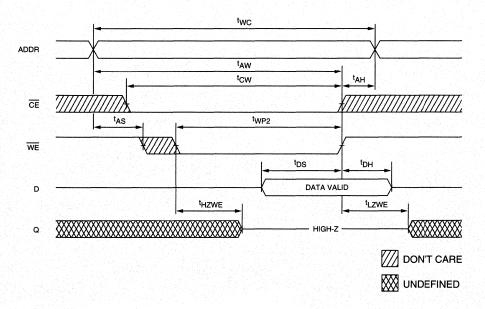

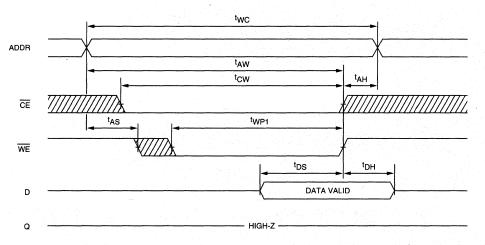

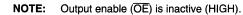

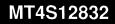

| WRITE cycle time                 | ⁺WC               | 8   |          | 10       |      | 12  |          | 15  |     | 20              |     | 25  |     | 35  |          | ns    |                             |

| Chip Enable to end of write      | <sup>t</sup> CW   | 8   |          | 9        |      | .10 |          | 12  |     | 15              |     | 20  |     | 25  |          | ns    |                             |

| Address valid to end of write    | <sup>t</sup> AW   | 8   |          | 9        |      | 11  |          | 12  |     | 15              |     | 20  |     | 25  |          | ns    |                             |

| Address setup time               | <sup>t</sup> AS   | 0   |          | 0        |      | 0   |          | 0   |     | 0               |     | 0   | 2   | 0   |          | ns    |                             |

| Address hold from end of write   | tAH               | 0   |          | 0        |      | 0   |          | 0   |     | 0               |     | 0   |     | 0   |          | ns    |                             |

| WRITE pulse width                | <sup>t</sup> WP   | 7   |          | 8        | М. , | 9   |          | 12  |     | 15              |     | 18  |     | 20  |          | ns    |                             |

| Data setup time                  | <sup>t</sup> DS   | 5   |          | 6        |      | 7   |          | 8   |     | 10              |     | 10  |     | 12  |          | ns    |                             |

| Data hold time                   | <sup>t</sup> DH   | 0   |          | 0        |      | 0   |          | 0   |     | 0               |     | 0   |     | 0   |          | ns    |                             |

| Write disable to output in Low-Z | <sup>t</sup> LZWE | 2   |          | 2        |      | 2   |          | 2   |     | 2               |     | 2   |     | 2   |          | ns    |                             |

| Write Enable to output in High-Z | <sup>t</sup> HZWE |     | 4        |          | 5    |     | 5        |     | 6   |                 | 8   |     | 8   |     | 8        | ns    | 6                           |

\*These specifications are preliminary.

# MT5C1601

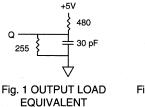

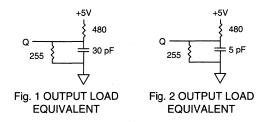

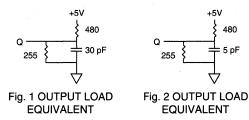

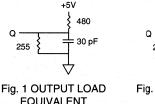

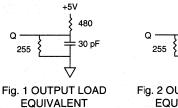

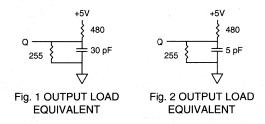

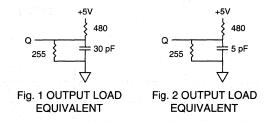

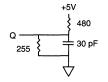

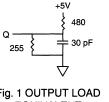

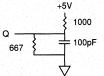

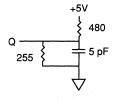

### **AC TEST CONDITIONS**

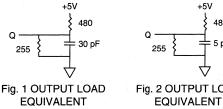

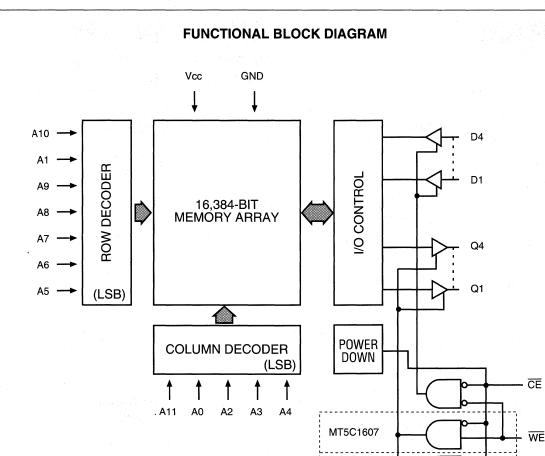

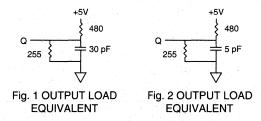

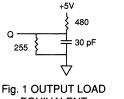

| Input pulse levels            | Vss to 3.0V           |

|-------------------------------|-----------------------|

| Input rise and fall times     | 5ns                   |

| Input timing reference levels | 1.5V                  |

| Output reference levels       | 1.5V                  |

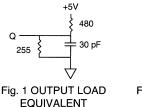

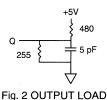

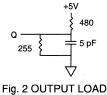

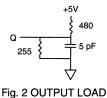

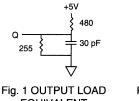

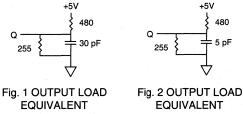

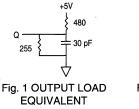

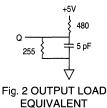

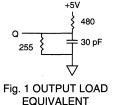

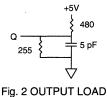

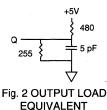

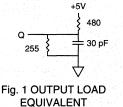

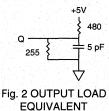

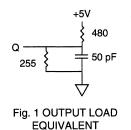

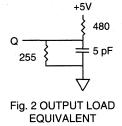

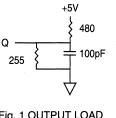

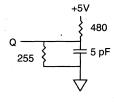

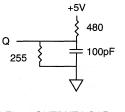

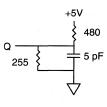

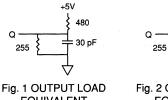

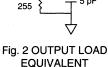

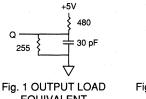

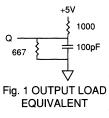

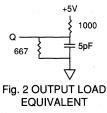

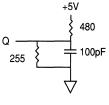

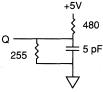

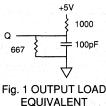

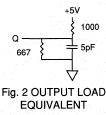

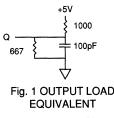

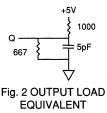

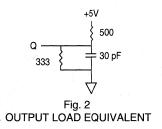

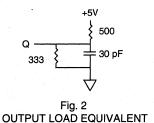

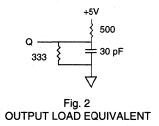

| Output load                   | . See Figures 1 and 2 |

### NOTES

- 1. All voltages referenced to Vss (GND).

- 2. -3V for pulse width < 20ns.

- 3. Icc is dependent on output loading and cycle rates.

- 4. This parameter is sampled.

- 5. Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- <sup>t</sup>HZCE and <sup>t</sup>HZWE are specified with CL = 5pF as in Fig. 2. Transition is measured ±500mV from steady state voltage.

- 7. At any given temperature and voltage condition, <sup>t</sup>HZCE is less than <sup>t</sup>LZCE and <sup>t</sup>HZWE is less than <sup>t</sup>LZWE.

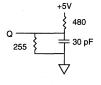

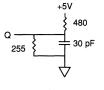

EQUIVALENT

FAST SRAM

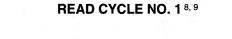

- 8.  $\overline{\text{WE}}$  is HIGH for READ cycle.

- 9. Device is continuously selected. All chip enables are held in their active state.

- 10. Address valid prior to or coincident with latest occurring chip enable.

- 11. <sup>t</sup>RC = Read Cycle Time.

- 12. Chip enable (CE) and write enable (WE) can initiate and terminate a WRITE cycle.

- 13. For automotive, industrial and extended temperature specifications, refer to page 1-171.

- 14. Typical values are measured at 5V, 25°C and 20ns cycle time.

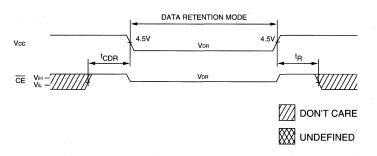

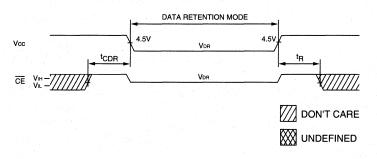

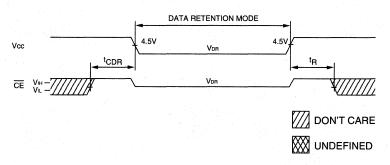

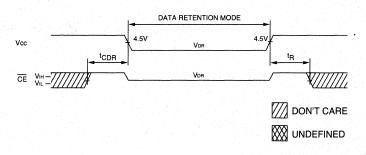

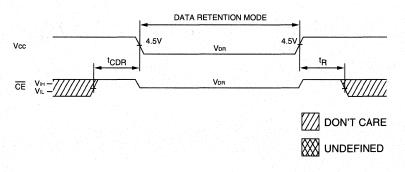

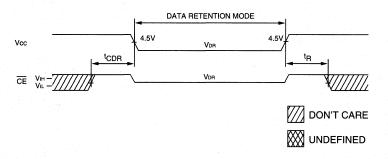

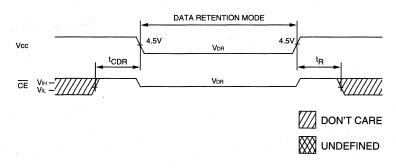

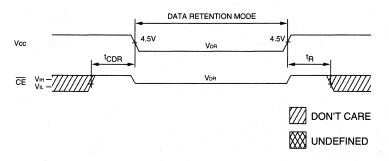

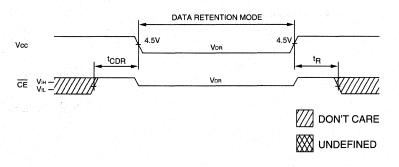

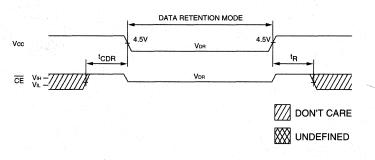

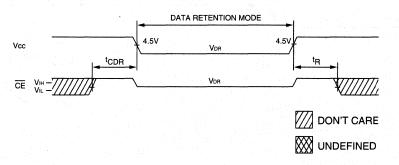

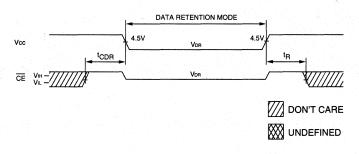

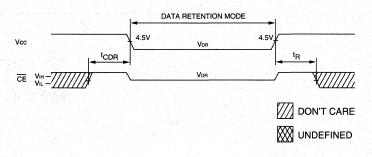

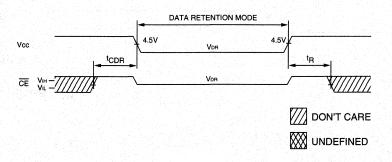

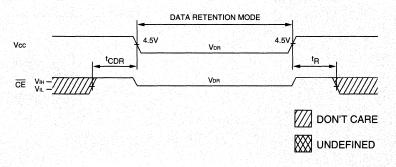

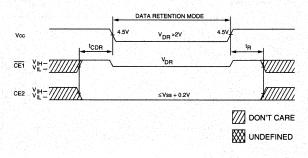

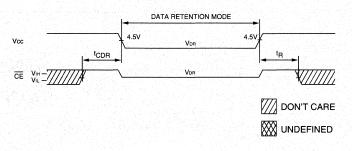

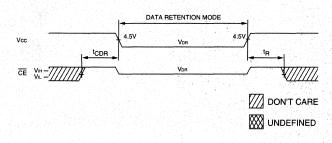

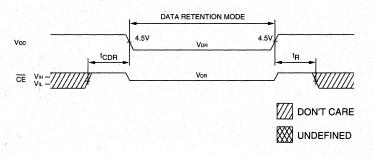

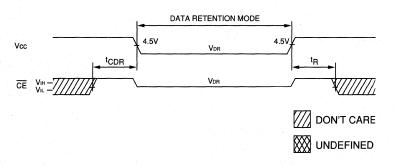

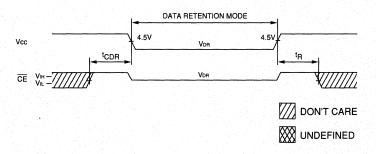

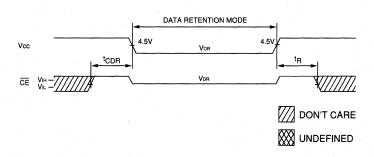

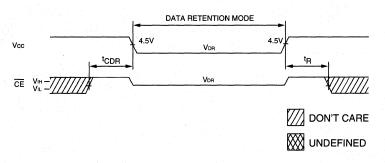

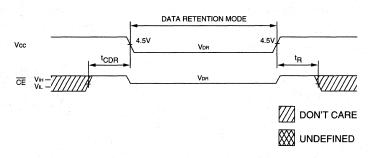

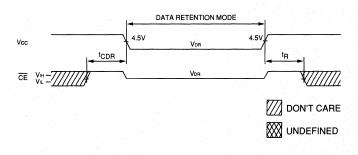

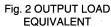

### DATA RETENTION ELECTRICAL CHARACTERISTICS (L Version Only)

| DESCRIPTION                             | CONDITIONS                                                 |          | SYMBOL           | MIN             | TYP | MAX | UNITS | NOTES |

|-----------------------------------------|------------------------------------------------------------|----------|------------------|-----------------|-----|-----|-------|-------|

| Vcc for Retention Data                  |                                                            |          | Vdr              | 2               |     |     | V     |       |

| Data Retention Current                  | $\overline{CE} \ge (Vcc - 0.2V)$ $V_{IN} \ge (Vcc - 0.2V)$ | Vcc = 2V | ICCDR            |                 | 95  | 250 | μA    |       |

| Data Netention Current                  | or $\leq 0.2V$                                             | Vcc = 3V |                  |                 | 125 | 400 | μA    |       |

| Chip Deselect to Data<br>Retention Time |                                                            |          | <sup>t</sup> CDR | 0               |     |     | ns    | 4     |

| Operation Recovery Time                 | -                                                          |          | <sup>t</sup> R   | <sup>t</sup> RC |     |     | ns    | 4, 11 |

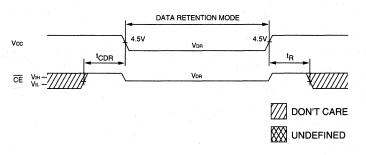

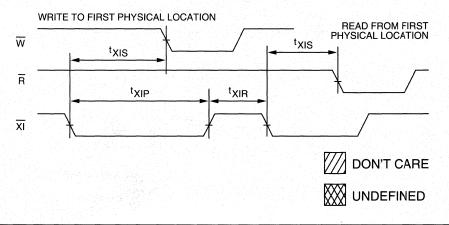

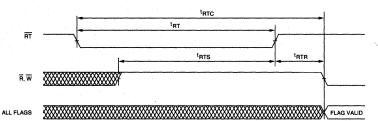

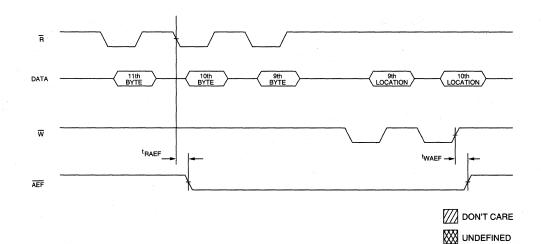

### LOW Vcc DATA RETENTION WAVEFORM

FAST SRAM

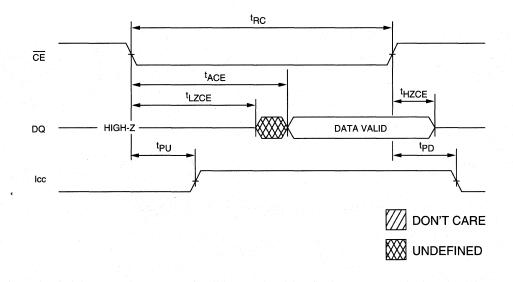

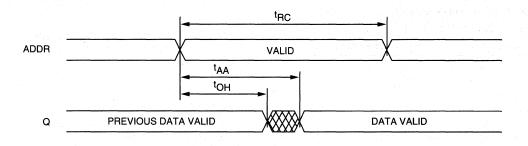

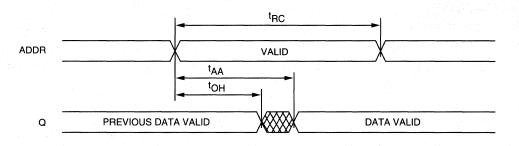

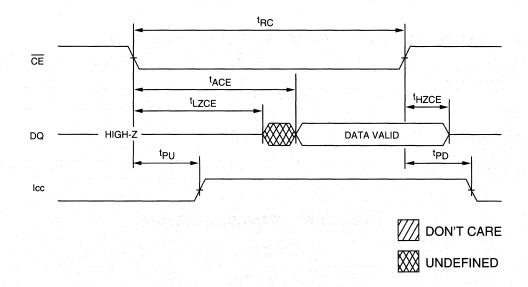

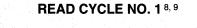

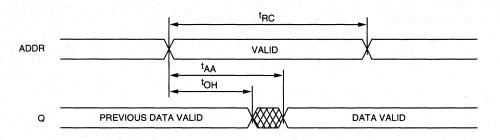

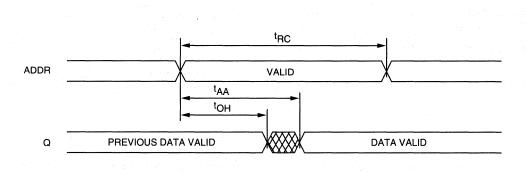

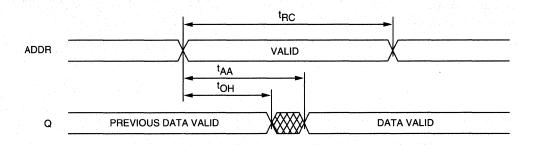

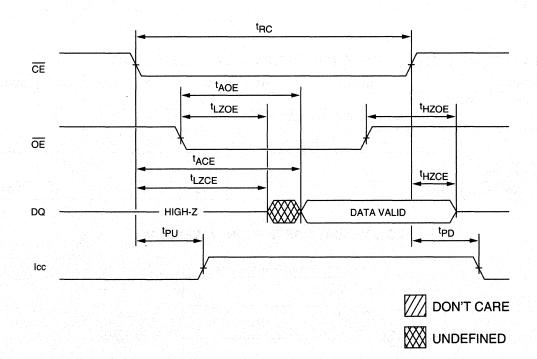

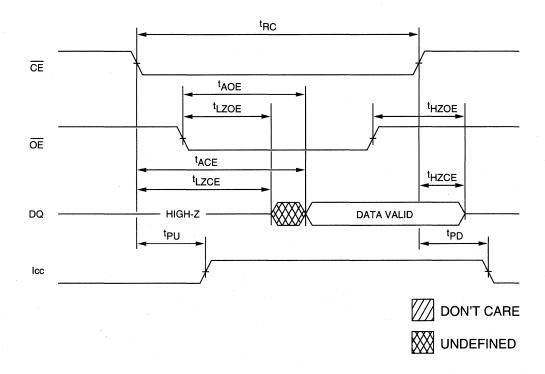

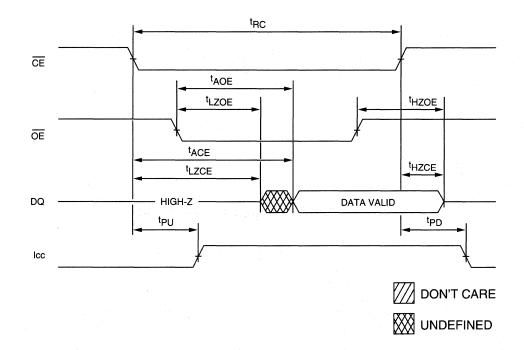

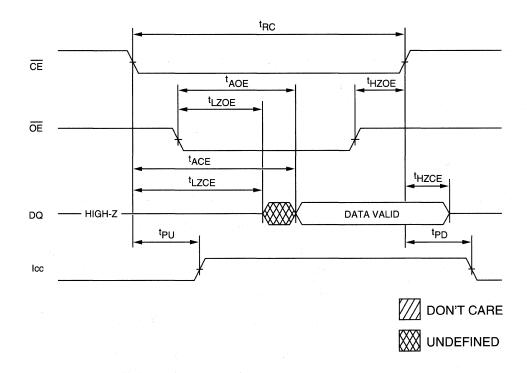

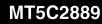

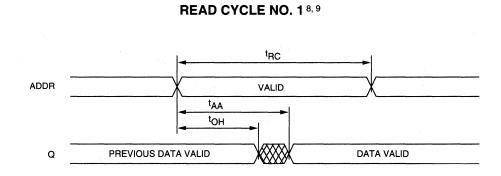

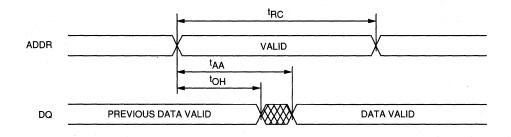

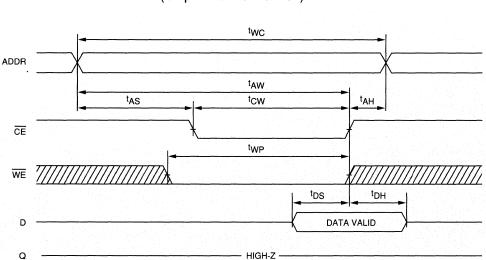

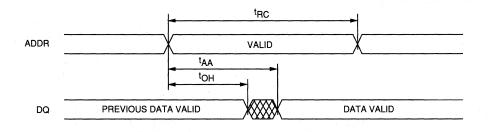

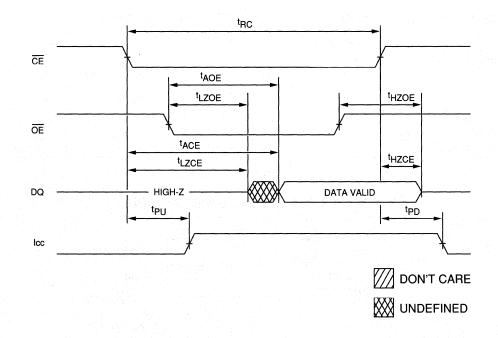

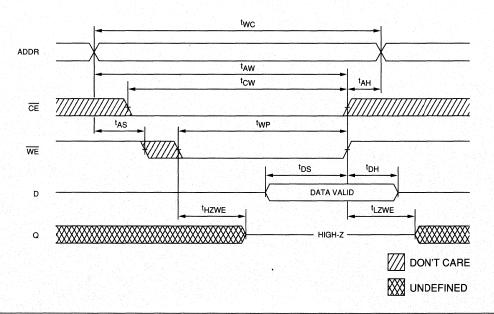

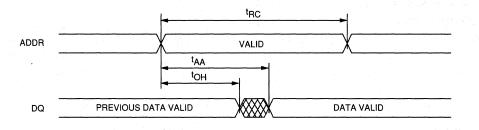

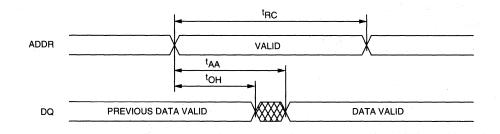

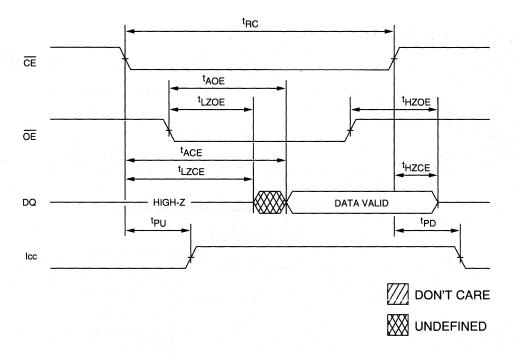

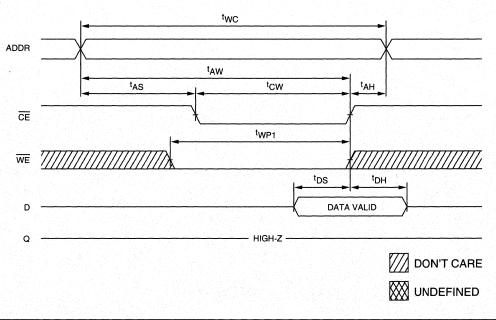

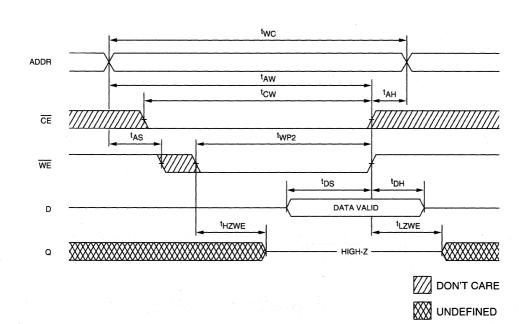

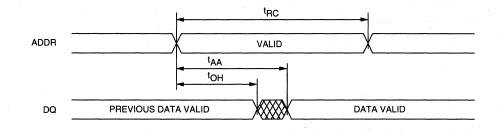

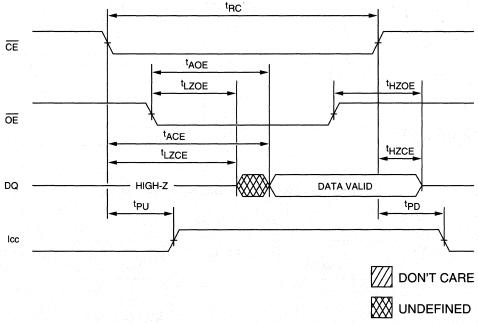

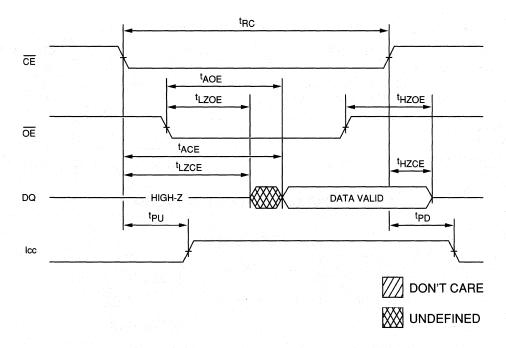

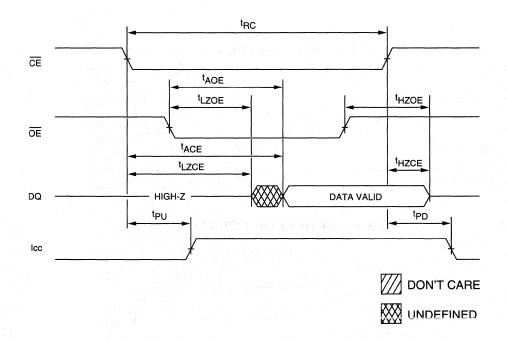

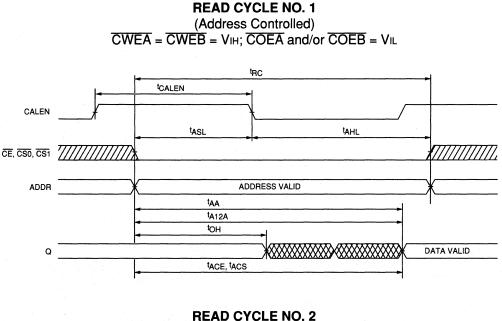

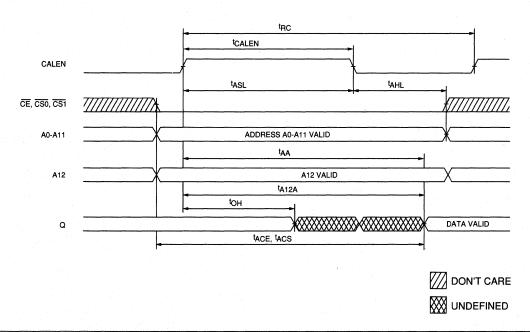

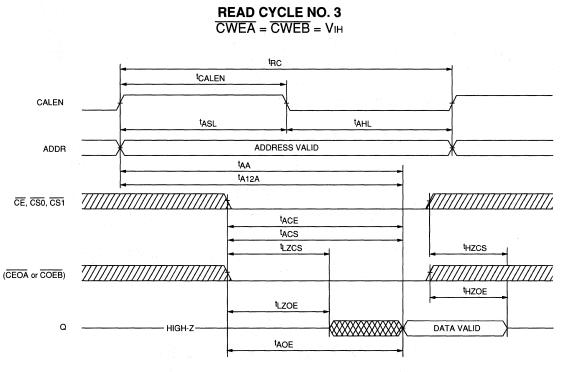

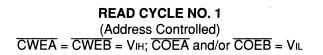

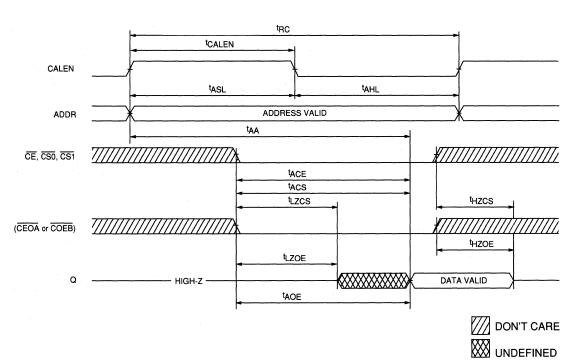

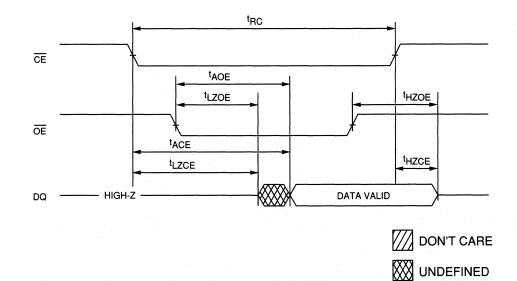

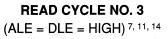

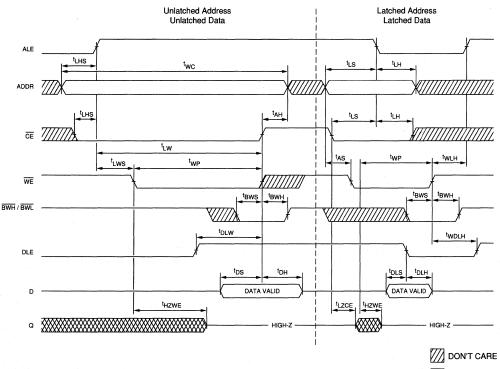

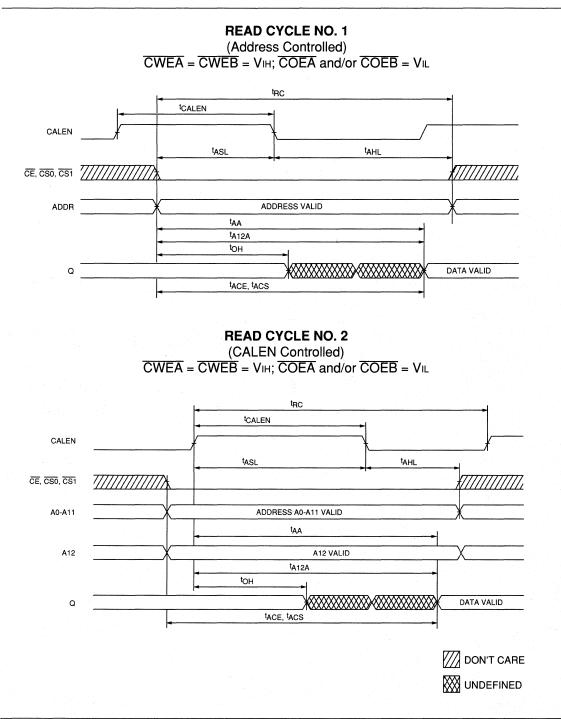

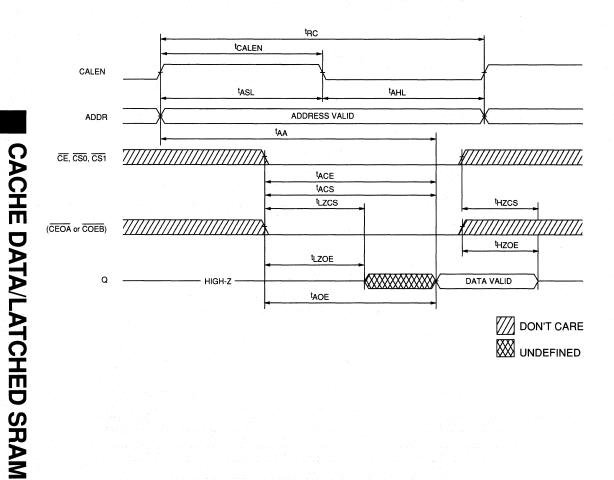

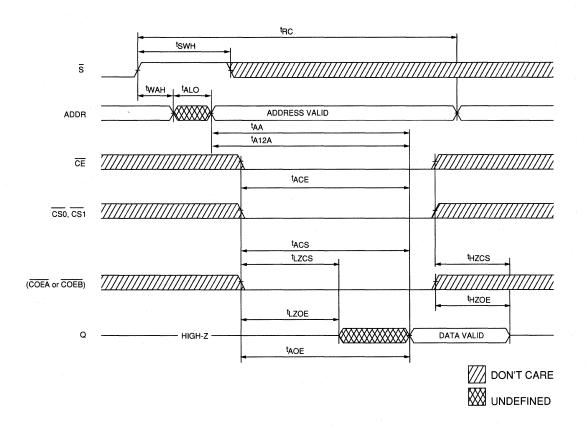

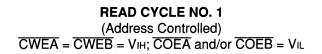

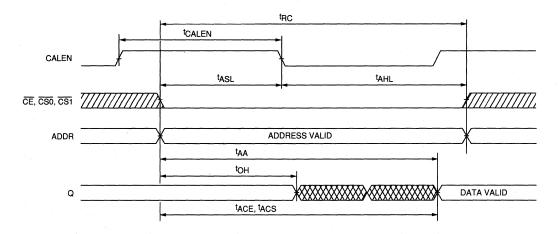

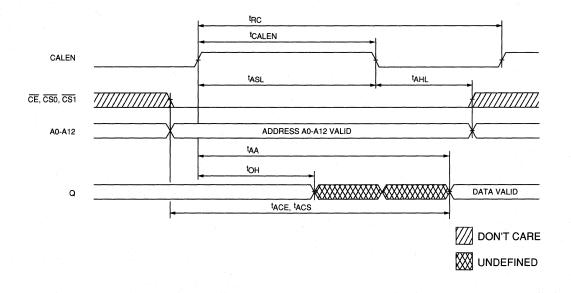

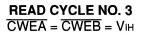

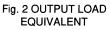

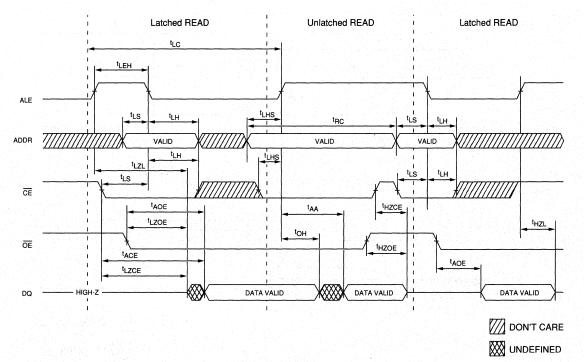

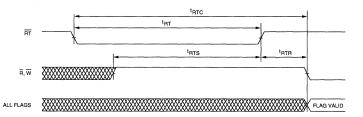

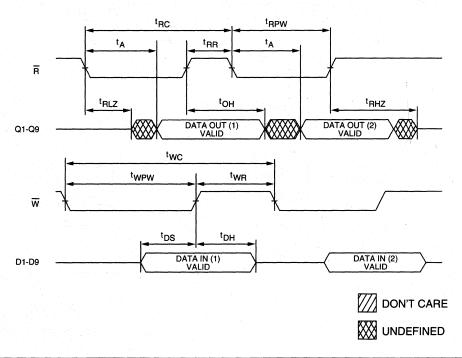

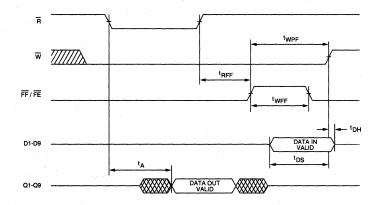

### READ CYCLE NO. 1<sup>8,9</sup>

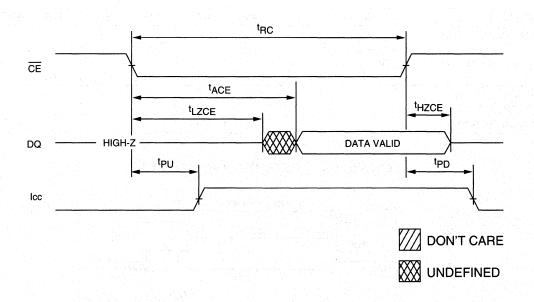

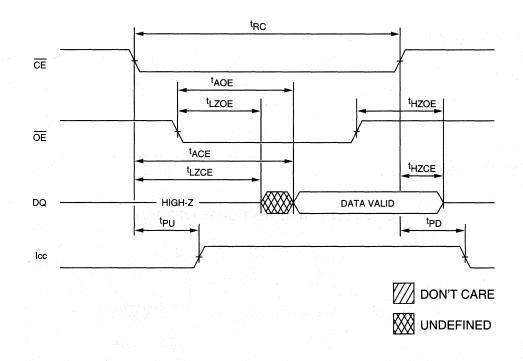

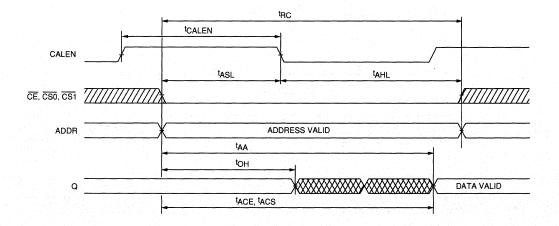

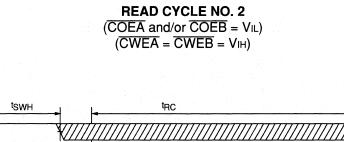

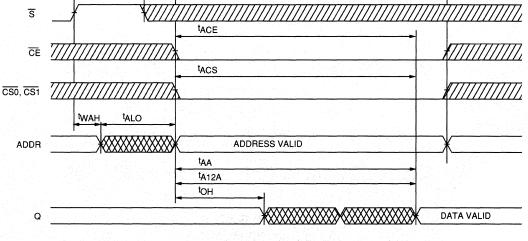

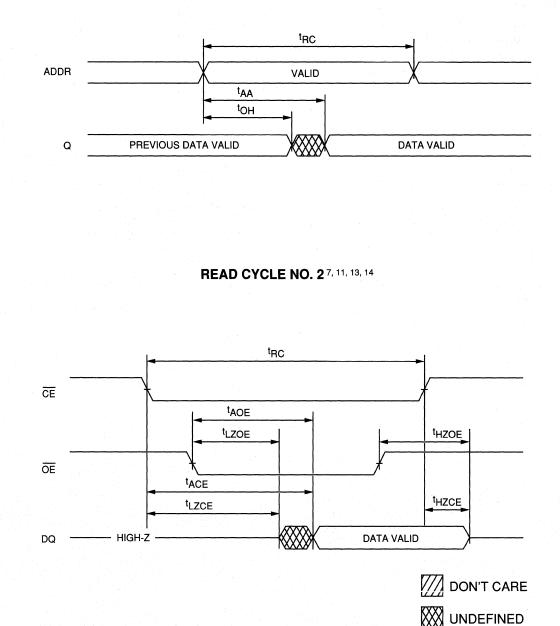

READ CYCLE NO. 27, 8, 10

.

# MT5C1601

FAST SRAM

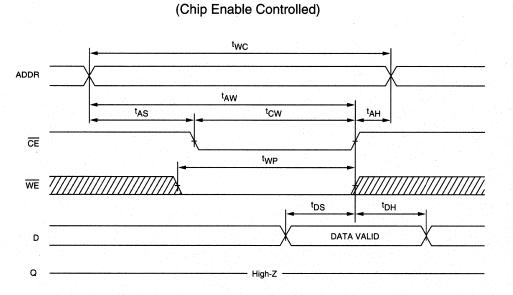

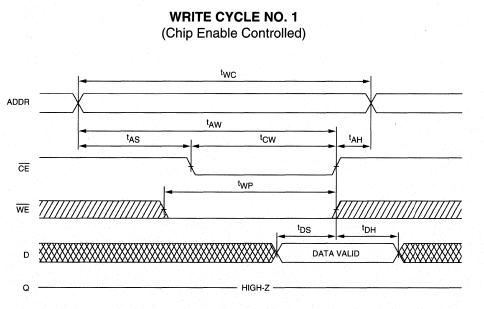

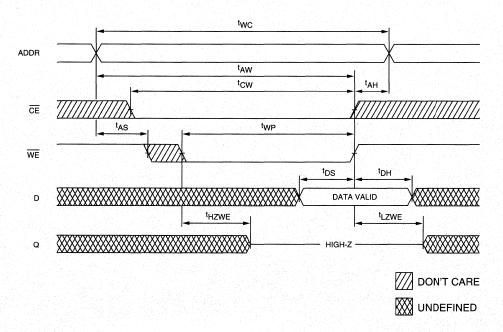

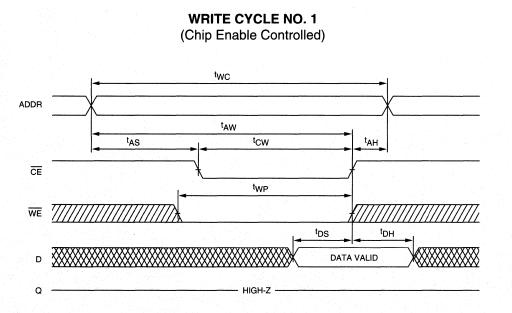

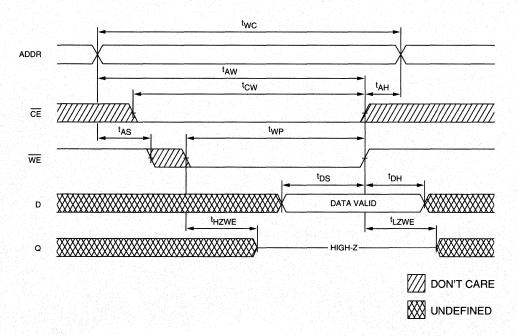

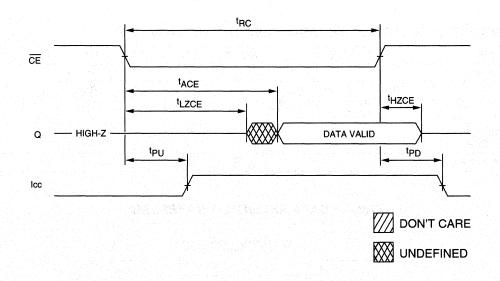

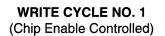

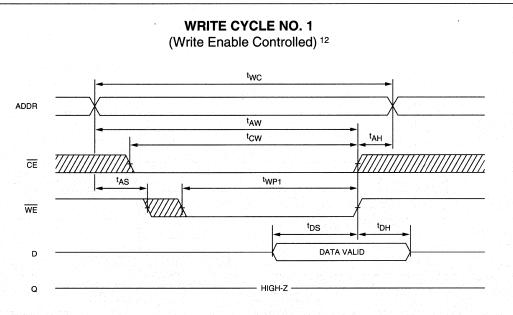

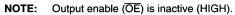

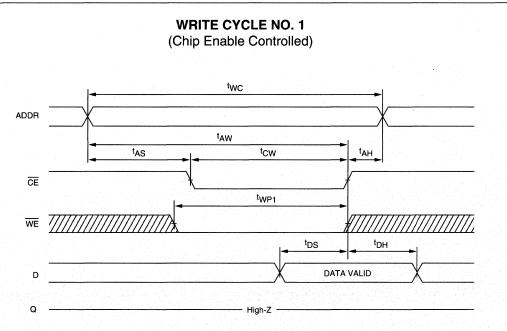

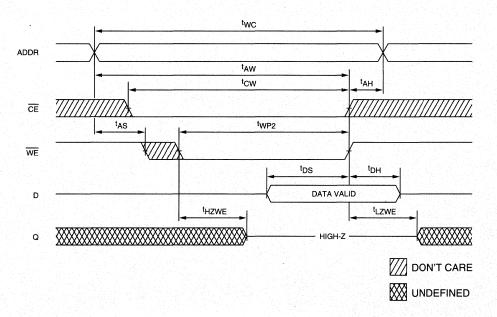

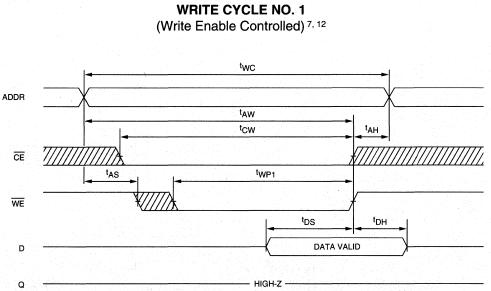

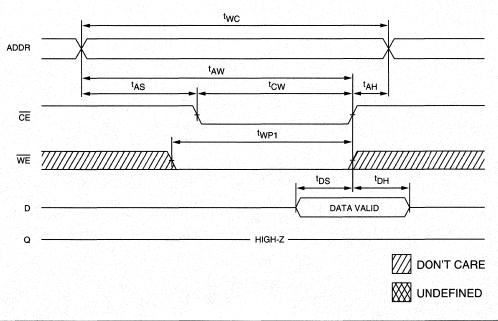

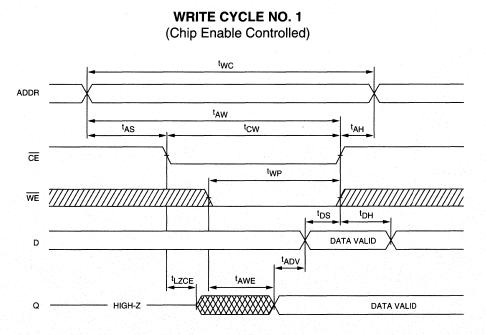

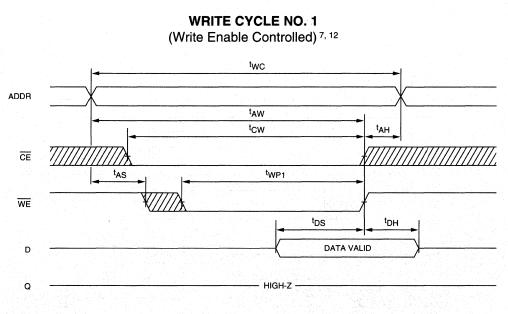

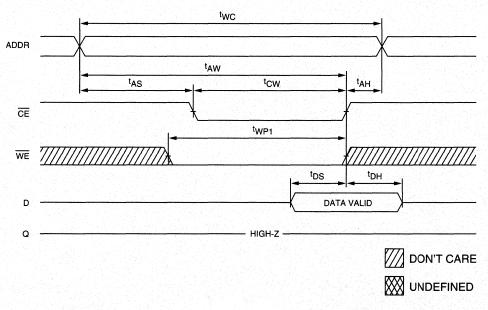

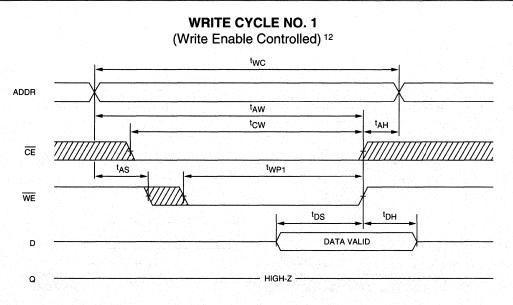

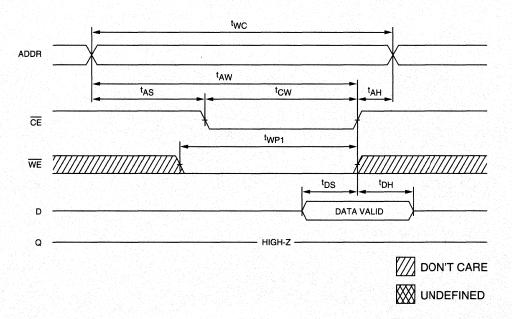

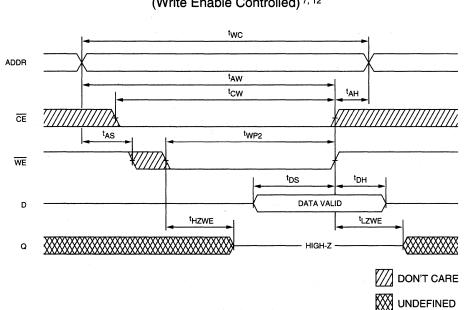

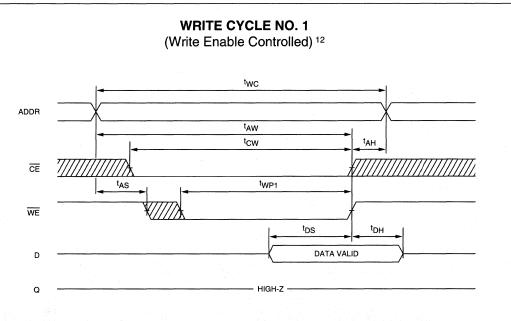

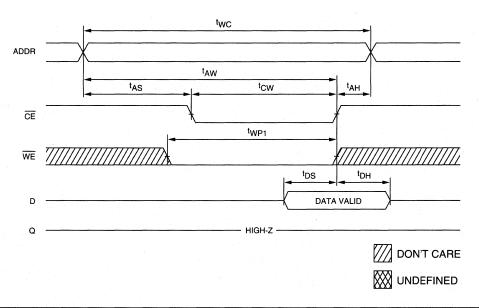

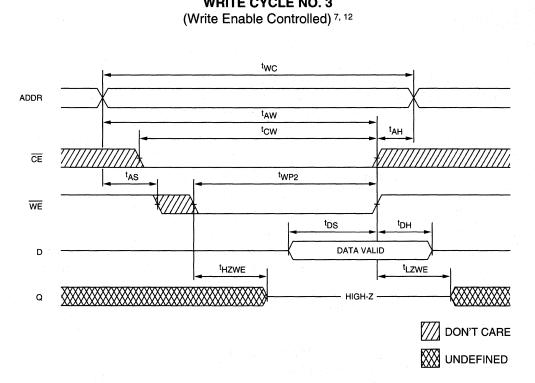

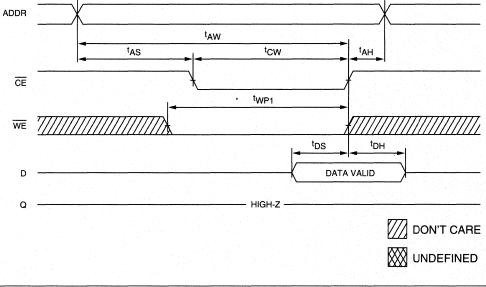

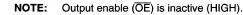

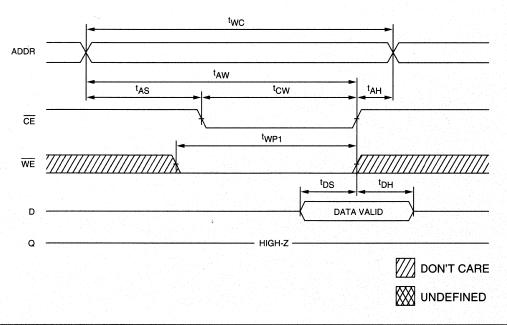

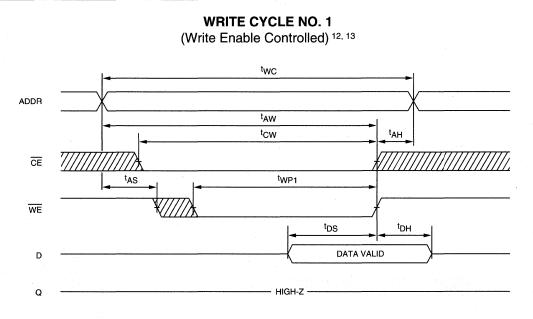

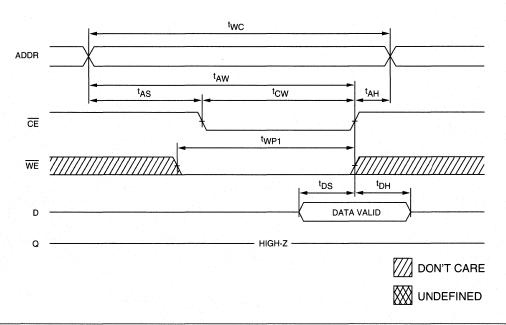

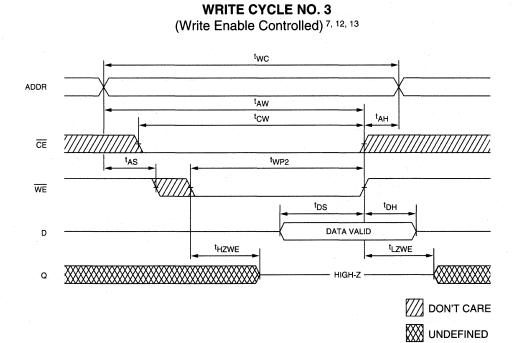

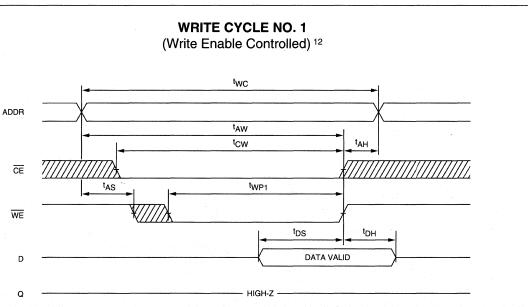

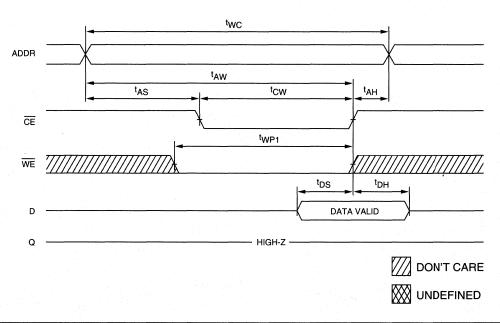

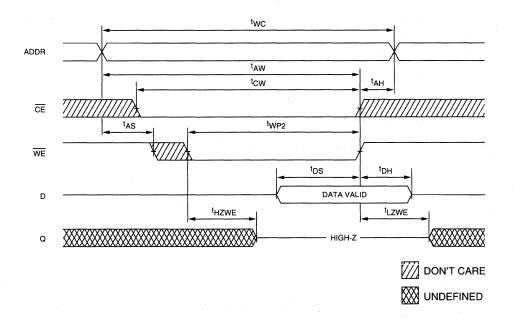

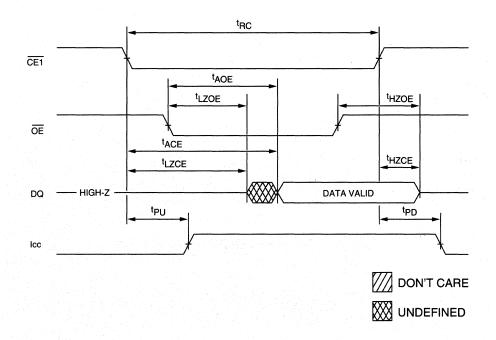

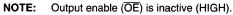

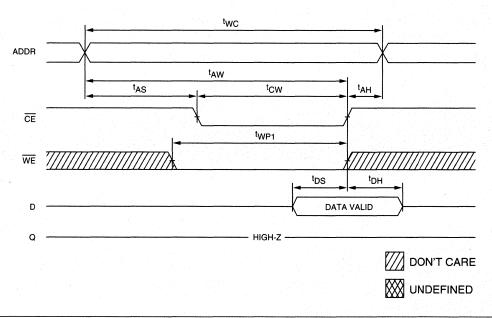

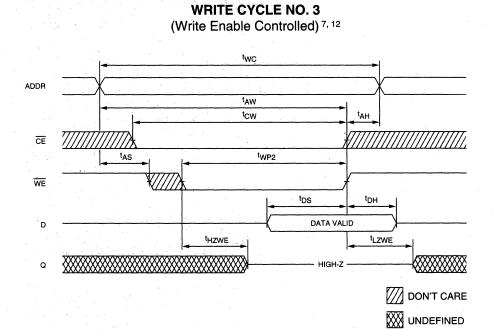

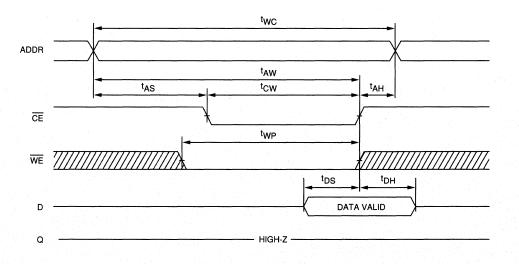

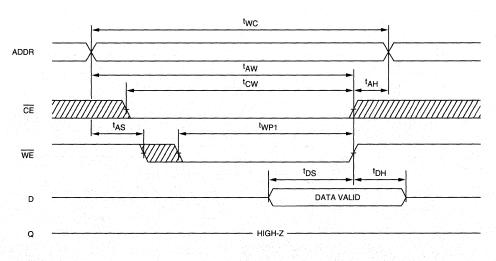

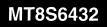

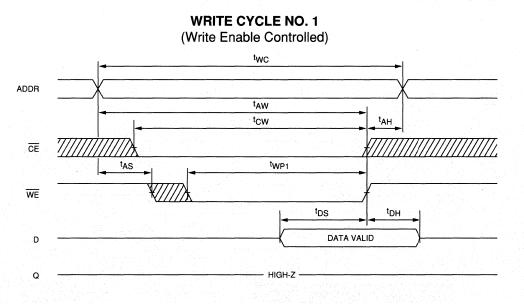

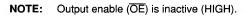

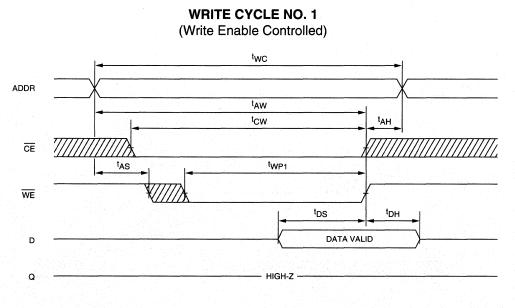

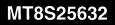

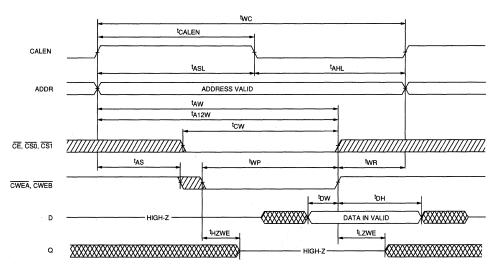

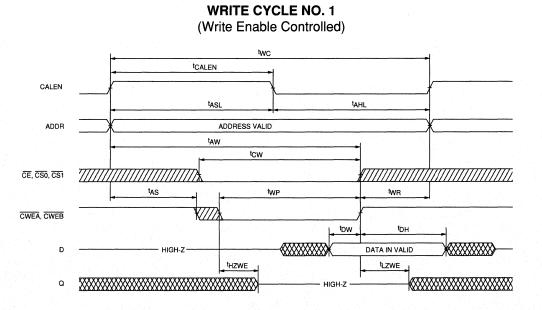

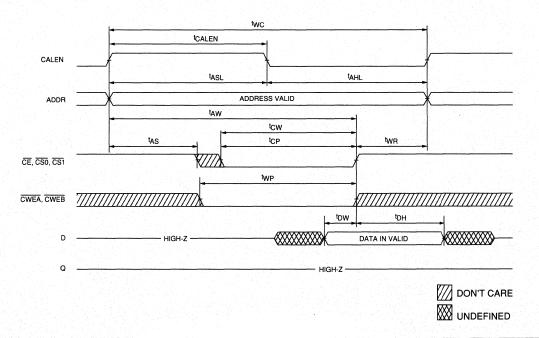

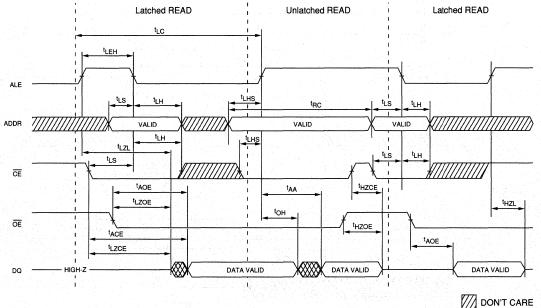

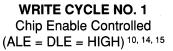

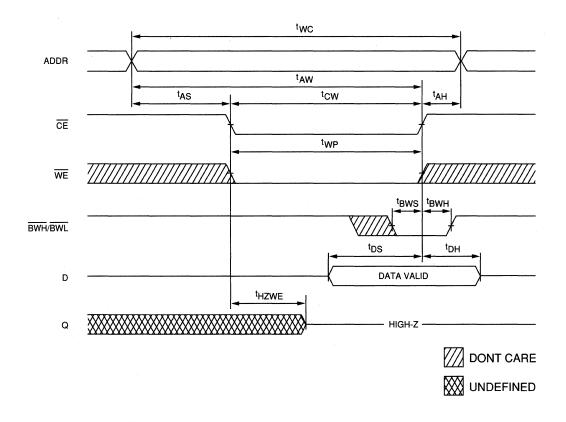

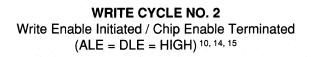

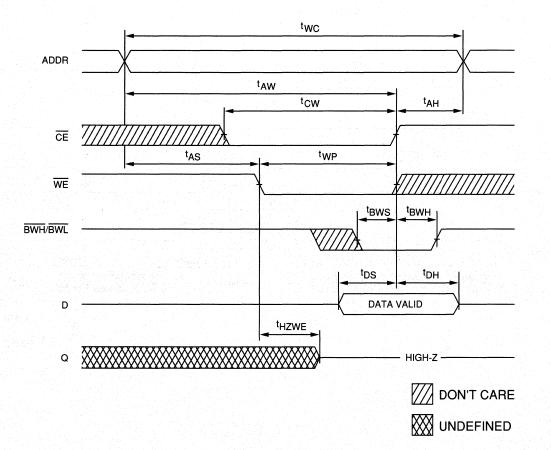

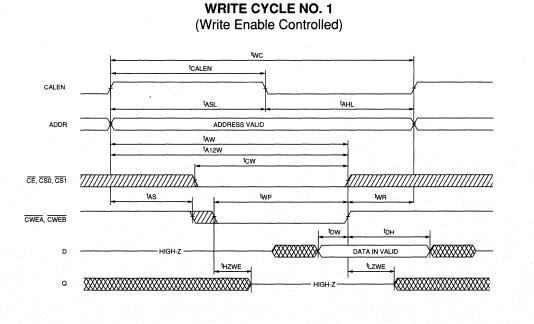

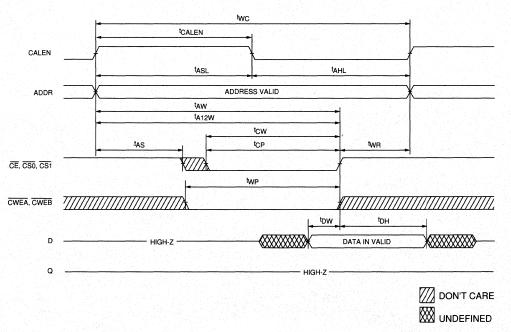

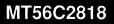

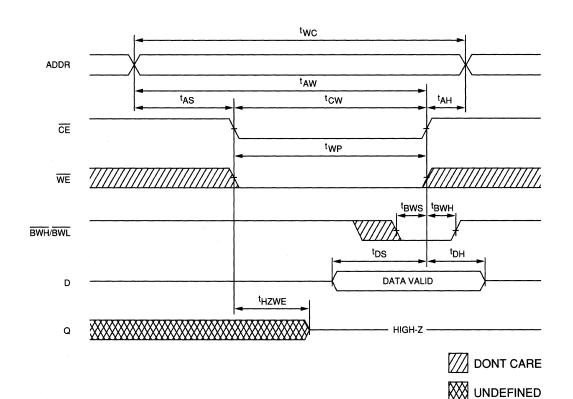

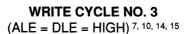

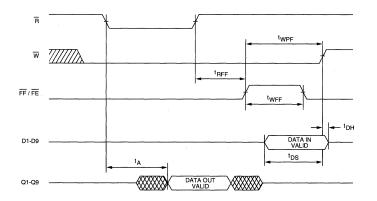

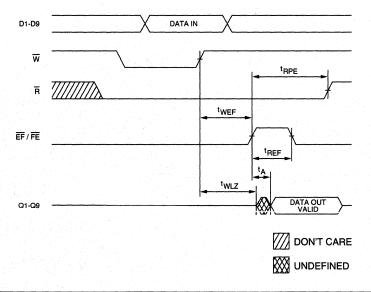

WRITE CYCLE NO. 1

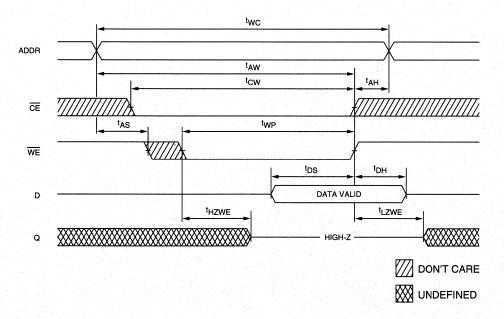

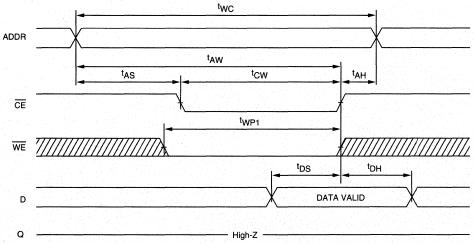

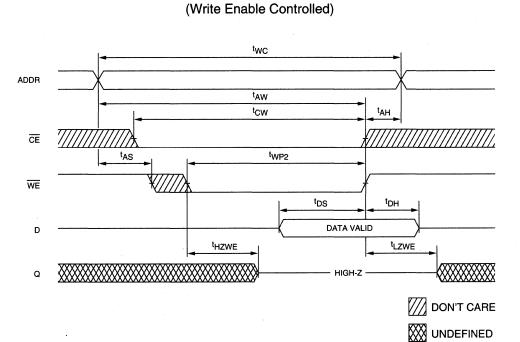

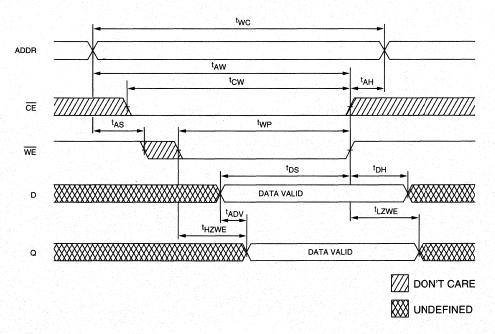

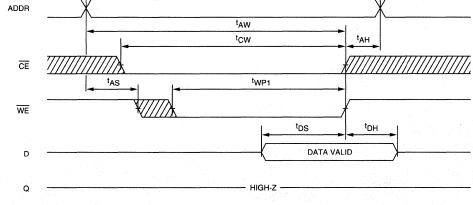

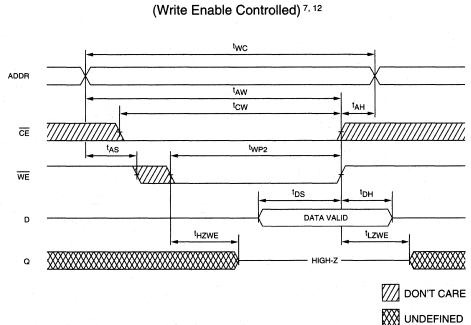

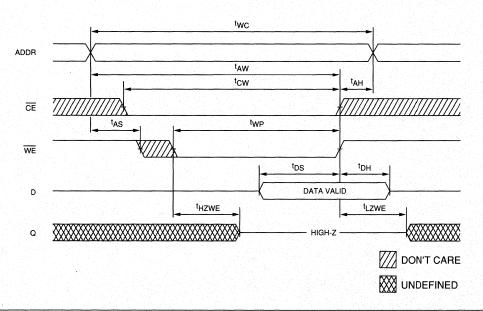

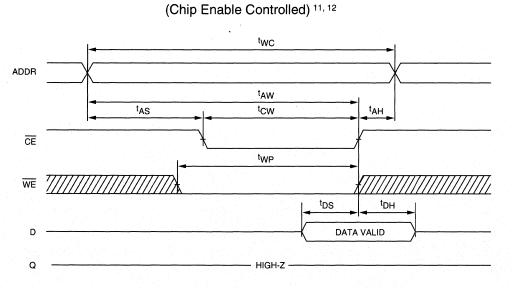

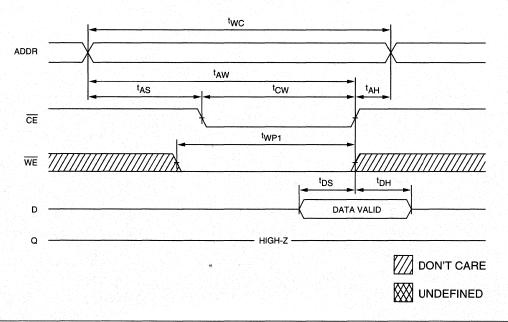

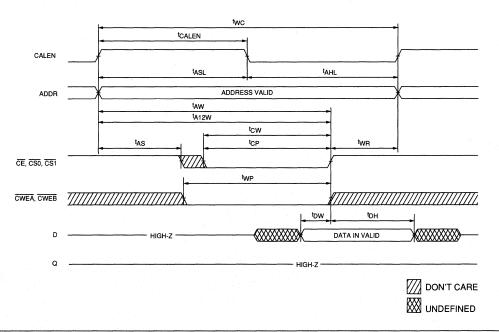

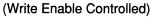

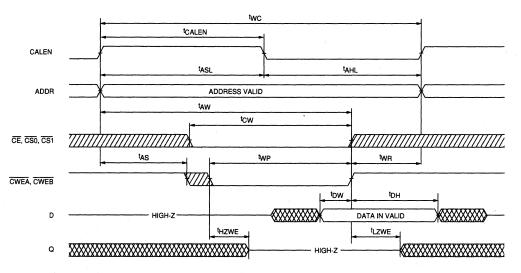

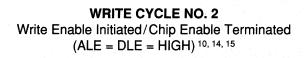

WRITE CYCLE NO. 2 (Write Enable Controlled) 7, 12

1-7

### MT5C6401

FAST SRAM

SRAM

# 64K x 1 SRAM

| FEATURES<br>• High speed: 8, 10, 12, 15, 20, 25 an            | d 35ns            | PIN ASSIGNMENT (Top View)                                                                                                                                                        |

|---------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>High-performance, low-power, C</li> </ul>            |                   | PIN ASSIGNMENT (TOP VIEW)                                                                                                                                                        |

| process                                                       | vico double-metai |                                                                                                                                                                                  |

| <ul> <li>Single +5V ±10% power supply</li> </ul>              |                   | 22-Pin DIP                                                                                                                                                                       |

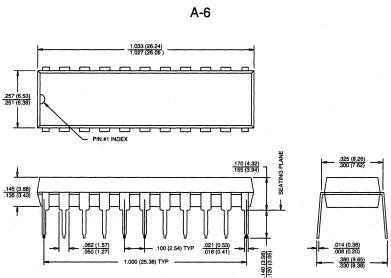

| • Easy memory expansion with CE                               | option            | (A-6)                                                                                                                                                                            |

| <ul> <li>All inputs and outputs are TTL co</li> </ul>         | mpatible          |                                                                                                                                                                                  |

| An inputs and outputs are TTE co                              | inputible         | A0 [1 22] Vcc                                                                                                                                                                    |

| OPTIONS M                                                     | ARKING            | [11] 제 이 문제 가슴에 가슴 이 집에 가슴 가슴 집에 다 가슴                                                                                                        |

|                                                               | AKKING            | A1 [] 2 21 [] A15                                                                                                                                                                |

| • Timing                                                      |                   | A2 [] 3 20 ]] A14                                                                                                                                                                |

| 8ns access (preliminary)                                      | - 8               | A3 [] 4 19 [] A13                                                                                                                                                                |

| 10ns access                                                   | -10               | A4 [] 5 18 [] A12                                                                                                                                                                |

| 12ns access                                                   | -12               | [19] - 이상 10, 10, 10, 10, 10, 10, 10, 10, 10, 10,                                                                                                                                |

| 15ns access                                                   | -15               | A5 [ 6 17 ] A11                                                                                                                                                                  |

| 20ns access                                                   | -20               | A6 [ 7 16 ] A10                                                                                                                                                                  |

| 25ns access                                                   | -25               | A7 [ 8 15 ] A9                                                                                                                                                                   |